Сумматоры и цифровые компараторы: принцип работы, схемы

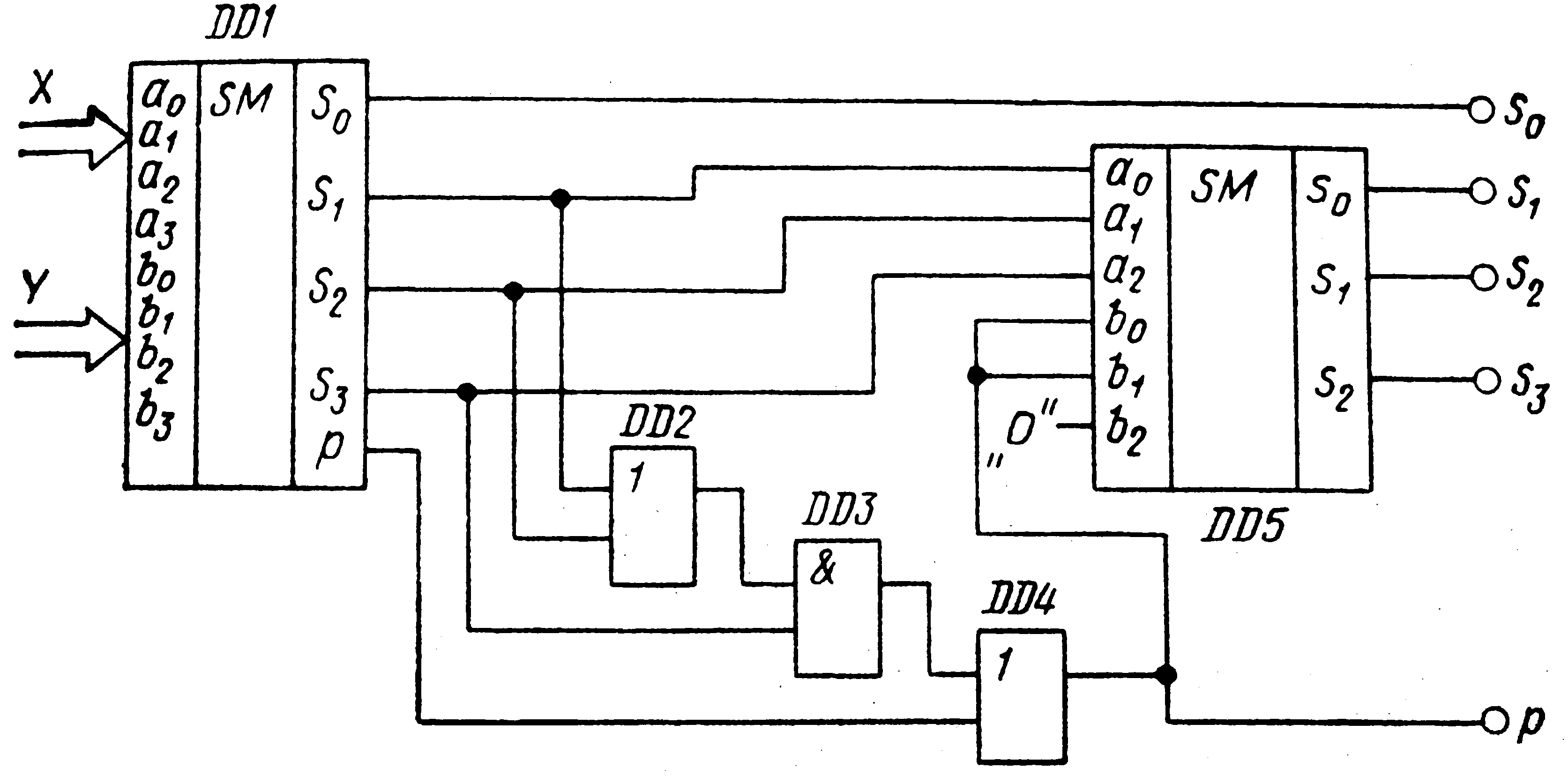

Сумматоры — это комбинационные устройства, предназначенные для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (см. рис. 3.48).

Сумматоры — это комбинационные устройства, предназначенные для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (см. рис. 3.48).

Цифровые сумматоры

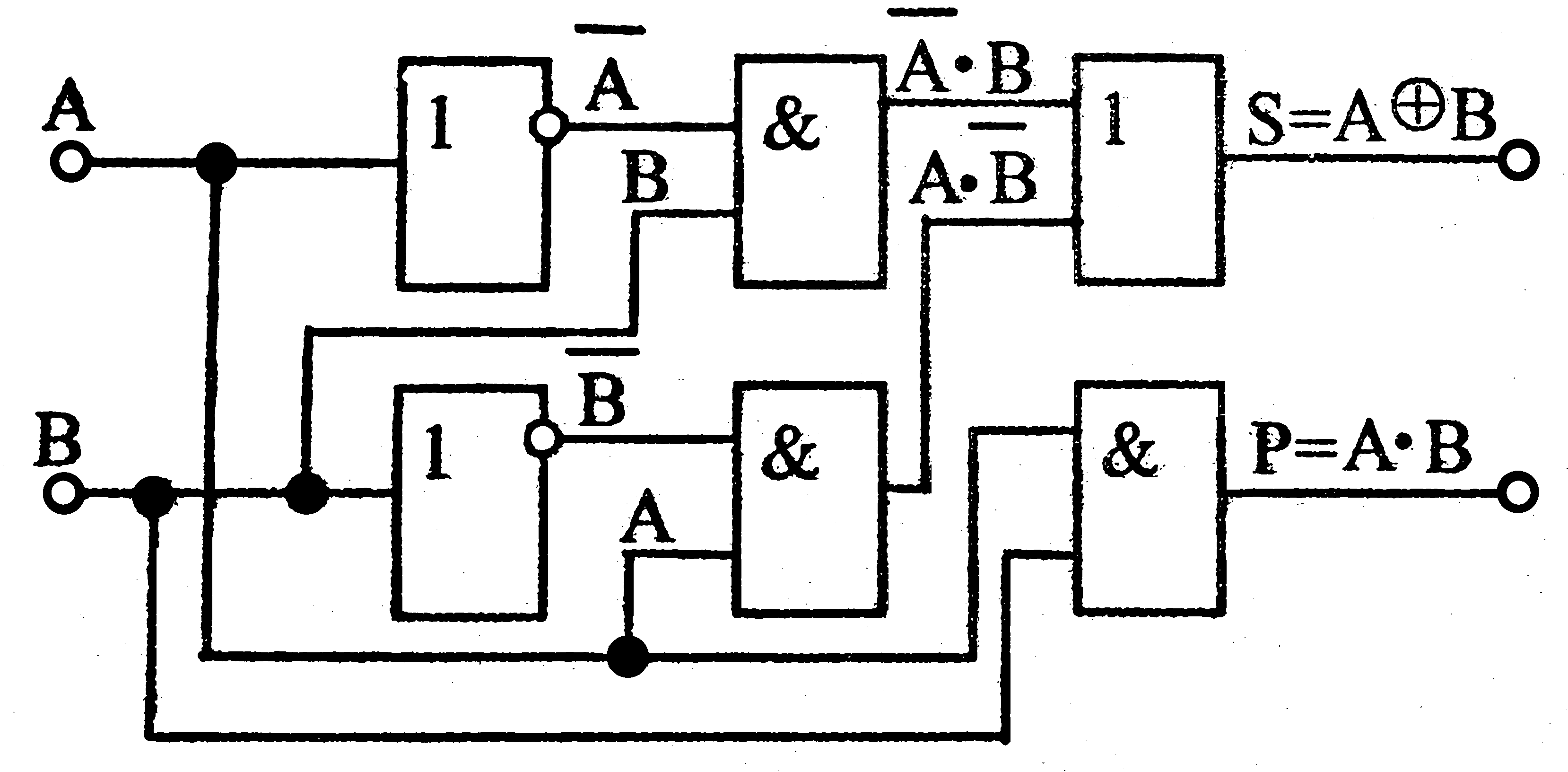

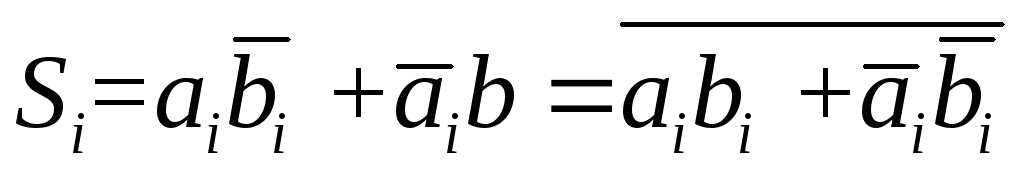

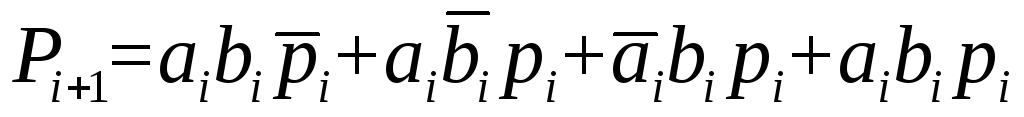

Работа устройства, реализующего таблицу истинность (рис. 3.48), описывается следующими уравнениями

S = А·В + А·В

Р = А·В

Очевидно, что по отношении: к столбцу S реализуется логическая функция «исключающее ИЛИ», т. е. S = А + В. Устройство, реализующее таблицу (рис. 3.48), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 3.49.

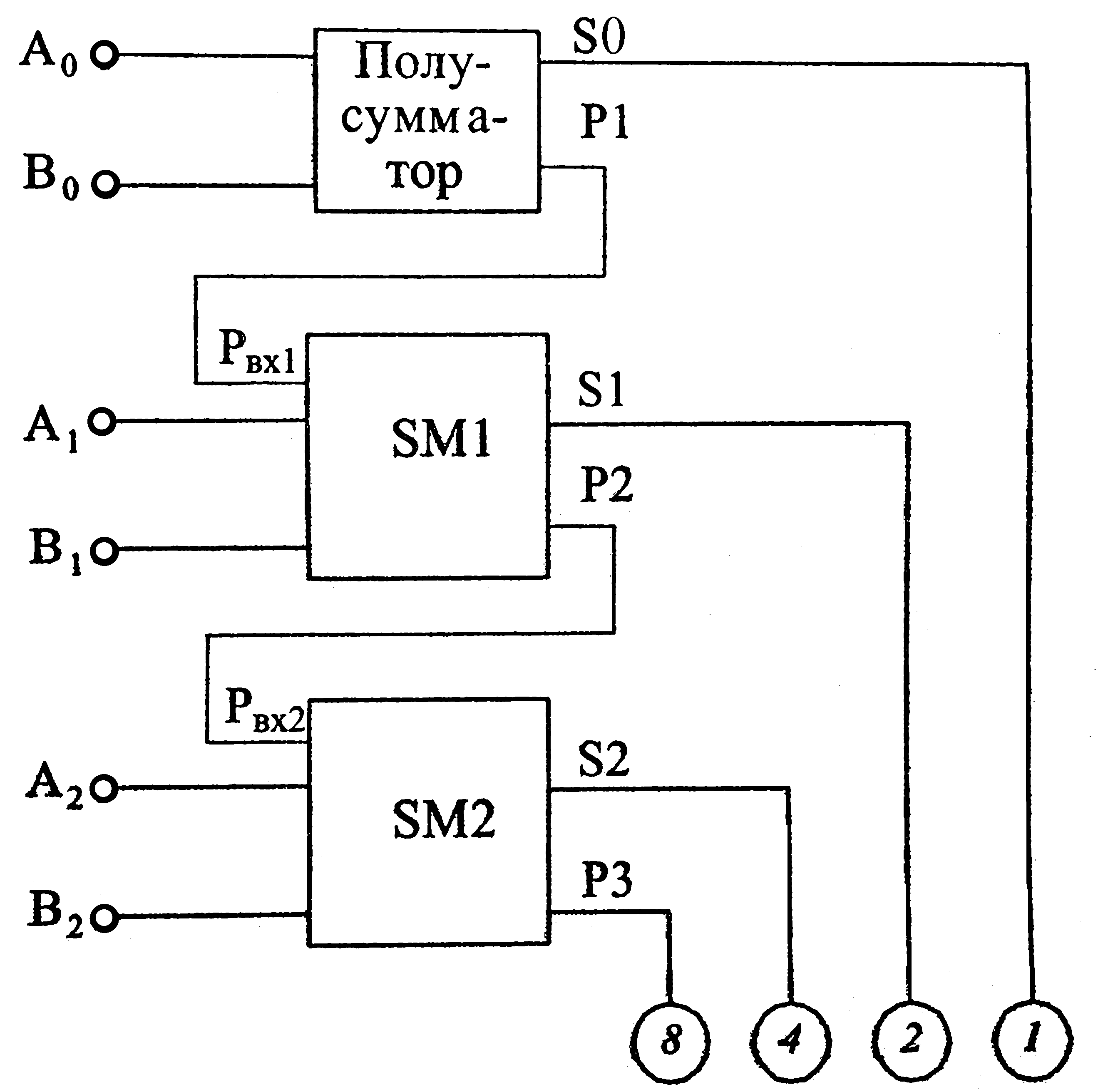

Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.

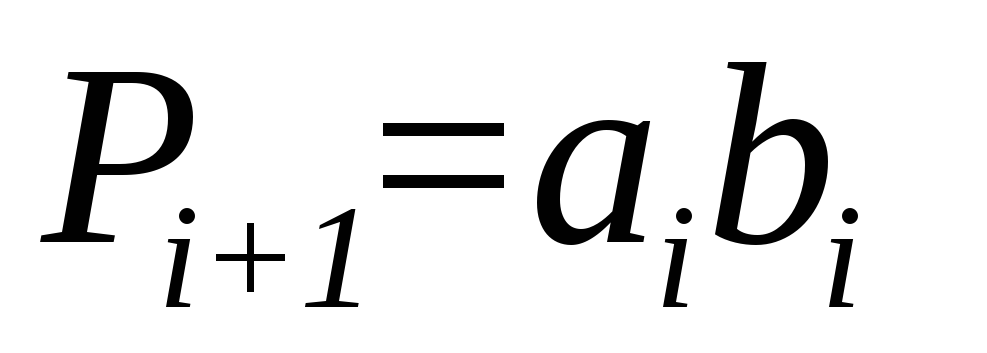

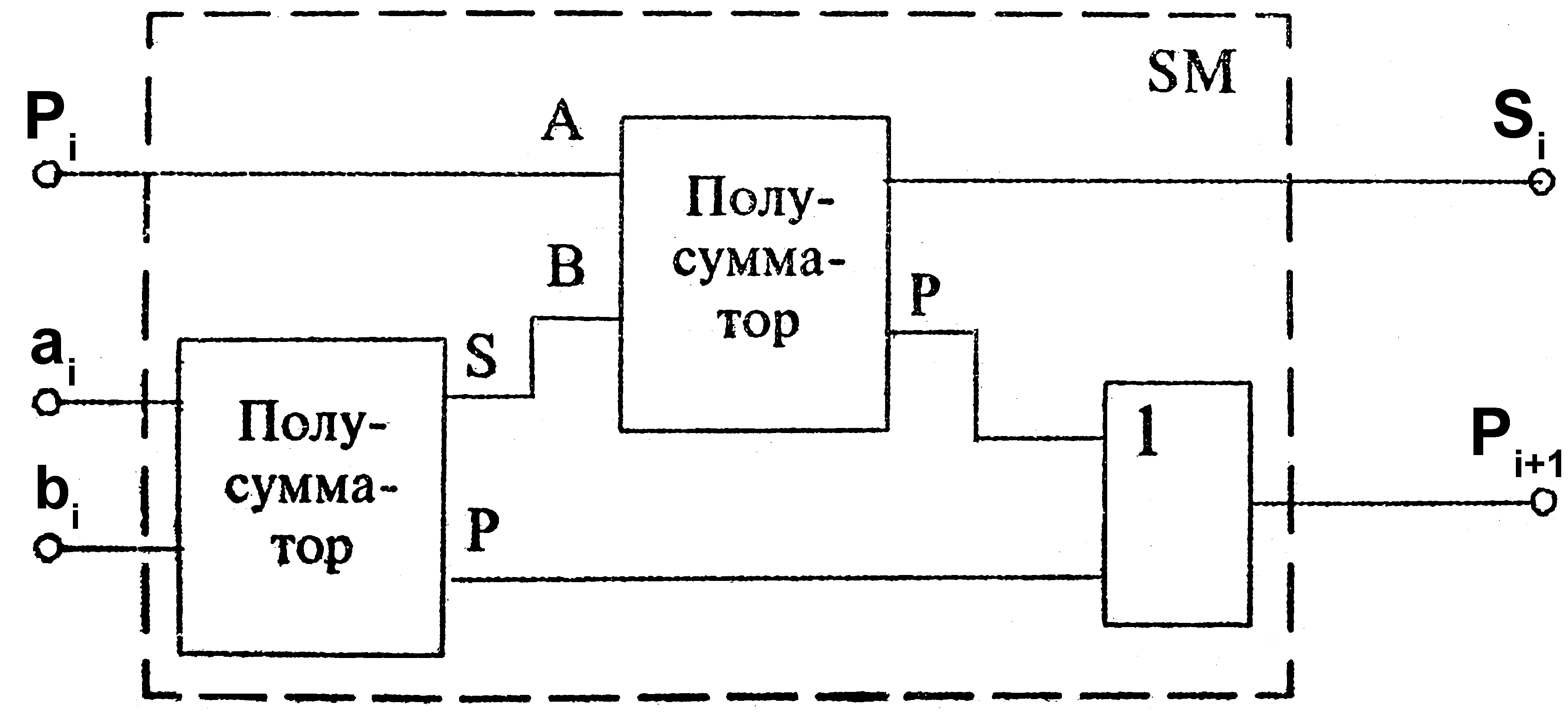

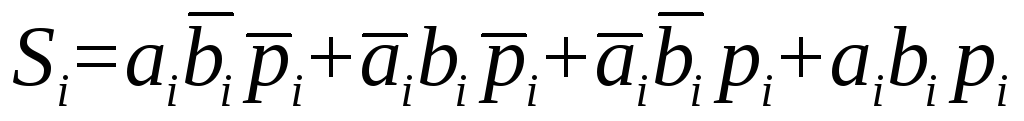

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство (рис. 3.50) называют полным сумматором и его можно представить как объединение двух полусумматоров (Рвх — дополнительный вход переноса). Сумматор обозначают через SM.

Цифровые компараторы

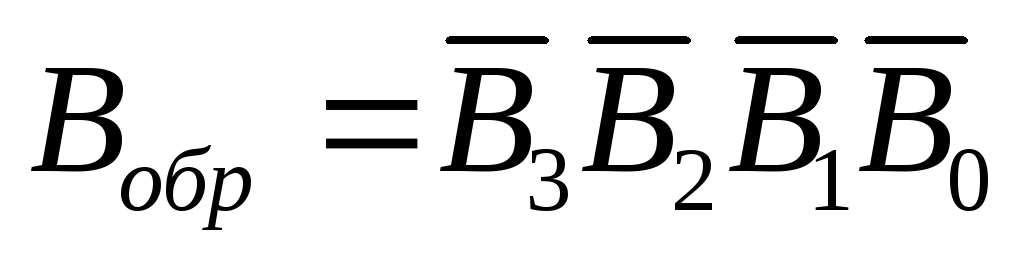

Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел A и B с одинаковым количеством разрядов либо вид неравенства A> B или A < B. Цифровые компараторы имеют три выхода.

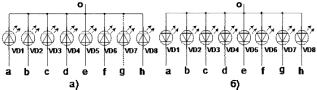

Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рис. 3.51).

Из анализа схемы следует, что если A= B, то F = 1, в противном случае, т. е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l.

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1 · F2 · F3 · F4 = 1. Если же F = 0, то А ≠ В.

Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > В1 (где А4 и В4 — старшие разряды чисел А и В). Очевидно, что если поменять местами А1 и B1, то будет выполняться неравенство А < В.

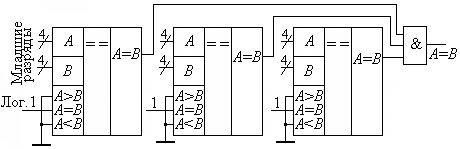

Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы А < В, А = В, А > В, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

pue8.ru

Компаратор схема на логических элементах

Компаратор – это устройство, предназначенное для сравнения каких-либо величин (от лат. comparare – «сравнивать»). Является операционным усилителем с большим коэффициентом умножения. Имеет входы: прямой и инверсный. При необходимости опорный сигнал может быть подключен к любому из них.

Как работает компаратор?

На один из входов подается постоянный сигнал, который называется опорным. Он используется как образец для сравнения. Ко второму поступает испытуемый сигнал. На выходе стоит транзистор, меняющий свое состояние в зависимости от условий:

- Напряжение прямого входа выше инверсного – транзистор открыт.

- Напряжение инверсного входа выше прямого – закрыт.

Соответственно, выходное напряжение меняется скачком от минимума до максимума, или наоборот.

Напряжение выходных каскадов соответствует входным уровням большинства цифровых микросхем. Это необходимо для случаев, когда компаратор – это формирователь импульса, управляющего работой логических элементов.

Применение компаратора

Используются в схемах измерения электрических сигналов и в аналогово-цифровых преобразователях. В логических цепях работают элементы «или» и «не», также являющиеся компараторами. Соответственно, использование этого компонента не ограничивается конкретными примерами, поскольку он применяется повсеместно.

Стоит отметить, что устройство сравнения можно сделать из любого операционного усилителя, но не наоборот. Коэффициент усиления компаратора достаточно высок. Соответственно, его входы очень чувствительны к разнице напряжений между ними. Расхождение в несколько милливольт значительно изменяет напряжение выхода.

Таким образом, компаратор позволяет наблюдать минимальные колебания уровней входных напряжений. Это делает его незаменимым элементом схем сравнения и измерительных приборов высокой точности:

- индикаторы уровня входящего сигнала;

- металлоискатели;

- микро- и милливольтметры;

- детекторы электромагнитных излучений;

- лабораторные датчики;

- компараторы массы;

- газоанализаторы.

Принцип действия аналогового компаратора

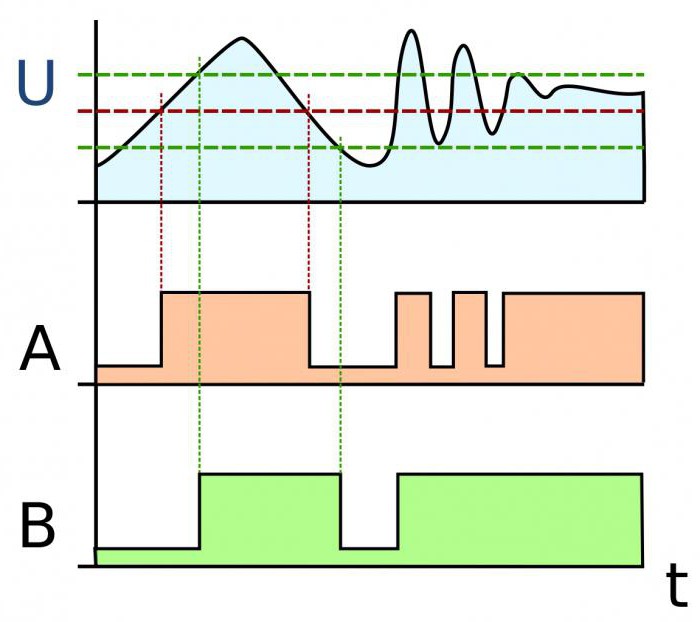

Аналоговый компаратор сравнивает непрерывные сигналы – входной измеряемый и входной опорный. Как работает устройство, показано на графике ниже.

При медленном изменении входного сигнала, происходит многократное переключение компаратора за малый отрезок времени. Такое явление называют «электронным дребезгом». Его наличие значительно снижает эффективность сравнения. Поскольку часто повторяющиеся смены состояния выхода, вводят оконечный транзистор в состояние насыщения.

Для уменьшения эффекта «электронного дребезга», в схему вводят ПОС – положительную обратную связь. Она обеспечивает гистерезис – небольшую разницу между уровнем напряжения включения и отключения. Некоторые компараторы имеют встроенную ПОС, что уменьшает количество дополнительных элементов построения конструкции. Например, при незначительной потери чувствительности, добиваются стабильной работы компаратора.

Особенности цифрового компаратора

Цифровой компаратор – это однобитный аналогово-цифровой преобразователь. Напряжение выхода представляет либо логический «0», либо «1». На вход может быть подан как аналоговый, так и цифровой сигнал. Устройство используется в качестве формирователя импульсов для сопряжения схем датчиков и устройств отображения. Может применяться для анализа спектра звукового или светового сигнала. Компаратор – это также логические элементы «или» и «не», используемые в вычислительной технике.

Теоретически при незначительно малых колебаниях уровня входного сигнала, может возникать состояние неопределенности выхода. На практике равенство измеряемого и опорного напряжений не наступает. Поскольку компаратор имеет ограниченный коэффициент усиления или положительную обратную связь.

Характерным примером является триггер Шмитта (ТШ). У него не совпадают уровни включения и выключения, что определяется ПОС. Это позволяет пренебречь дискретной помехой при работе компаратора.

Компаратор-микросхема

Промышленность выпускает компараторы в виде интегральных схем. Их использование позволяет создавать компактные приборы, с минимумом навесных элементов. Также преимущество малогабаритных деталей в незначительной длине соединительных проводников. В условиях повышенного электромагнитного излучения они являются приемными антеннами для всевозможных электрических помех.

Компаратор на операционном усилителе

У компараторов есть немалое сходство с операционными усилителями:

- коэффициент усиления;

- входное сопротивление;

- значение входных токов;

- состояние насыщения.

Чувствительность, по-другому разрешающая способность, – это специфический параметр. Она определяет точность сравнения. Характеризуется минимальной разностью сигналов, при которой происходит срабатывание компаратора. Ее значение у интегральных микросхем имеет сотен микровольт. Это несколько хуже, чем у компараторов на операционных усилителях.

Время переключения характеризует быстродействие компараторов. Определяется минимальным временем изменения выходного сигнала: от момента сравнения до момента срабатывания. Зависит от разности сигналов на входах. Значения времени переключения составляют десятки и сотни наносекунд.

Как сделать компаратор своими руками?

Кто умеет читать принципиальные схемы и паять, без труда соберет простейшие компараторы для использования в быту. Область применения весьма обширна. На них можно построить массу конструкций с минимальными затратами. Простейший компаратор – это операционный усилитель без положительной обратной связи.

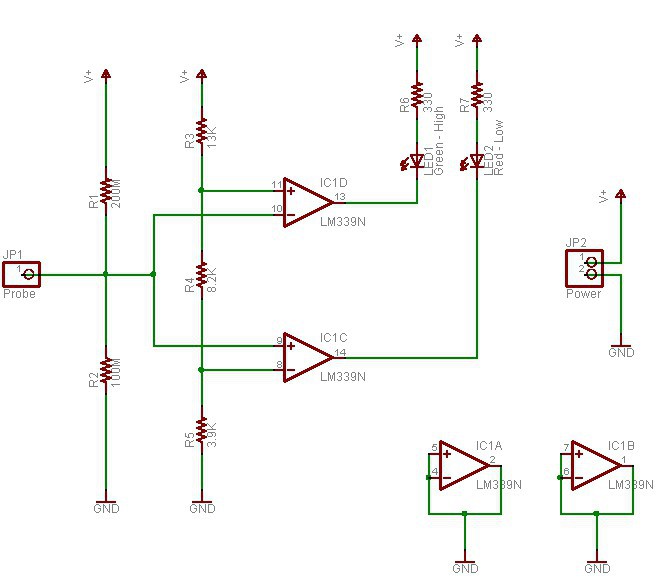

В качестве основы для компаратора используется ОУ серии LM339. Для контроля и наглядности работы схемы введены красный и зеленый индикаторы. При подключении питания на ОУ должен засветиться один из светодиодов, причем какой из них — неважно. Это определяется множеством факторов: сетевые наводки на схему, особенности партии и параметров ОУ. Даже если взять несколько одинаковых микросхем, получатся различные результаты.

Если входной сигнал близок к «0» – будет светиться зеленый, а если близкое к напряжению питания, то красный светодиод. Затем можно попробовать сменить логическое состояние компаратора, подав на один из входов напряжение равное, например, половине напряжения питания ОУ. Сигнал на выходе не зависит от абсолютного значения напряжений на прямом и инверсном входе. А только от разницы напряжений.

Данные опыты демонстрируют работу компаратора без ПОС. Такой компаратор может быть использован там, где не требуется особой точности измерений. Такими приборами являются бытовые термостаты, зарядные устройства для автомобильных аккумуляторов, устройства десульфатации (восстановления) автоаккумуляторов, фотореле.

Пример практического применения компаратора

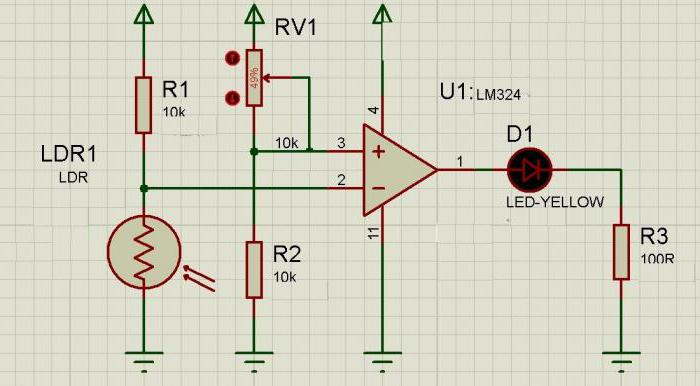

На принципиальной схеме представлен датчик освещенности.

Опорное напряжение задается резисторами RV1 и R2. При этом, RV1 служит регулятором чувствительности конструкции. Индикация реализована на светодиоде D1. Датчиком является элемент LDR1, который меняет омическое сопротивление в зависимости от освещенности. Собственно компаратор представлен операционным усилителем LM324. Это простое устройство демонстрирует то, как работает компаратор на практике.

Компараторы массы: понятие

Компаратор массы это устройство, предназначенное для уточнения разности значений массы гирь при контроле стандартов массы и веса, а также, для прецизионного взвешивания. Наиболее точные компараторы массы способны взвесить любой образец и сравнить его с иным, подобным ему. Происходит это на уровне атомов. Необходимость в таких устройствах возникает по причине несовершенства эталонных образцов мер веса и объема жидкости.

Примеры и использование устройств уточнения веса

Российским стандартом массы является платиновый цилиндр. Он был скопирован с французского образца 125 лет назад. За прошедшие годы, эталон потерял в виде окислов около 40 мкг от первоначального веса. Соответственно, его использование для нужд производств, с высокой точностью измерения массы сейчас затруднительно.

Был разработан новый стандарт массы. Ученые назначили таковым кремниевый шар с четным количеством атомов. Сейчас это наиболее точный вариант эталона килограмма. Его характеристики приняты международным сообществом для использования.

Созданный образец нуждается в многократном копировании. Так как современные направления в науке, особенно фармакология, биоинженерия, компьютерная электроника, нанотехнологические разработки требуют прецизионной точности измерений. Для таких областей науки и техники критичны сотые доли микрограмма. Эту задачу должен решить атомный компаратор массы – устройство способное определить разницу в несколько частиц.

Атомный компаратор использует для измерений опорный сигнал, полученный от высокоточного кварцевого генератора. Измеряемое напряжение берется с квантового дискриминатора, определяющего стабильность линии мельчайших частиц. Ее изменения вызываются расхождением в количестве атомов образца. Поэтому сейчас – это самый точный прибор измерения.

Существуют и менее точные компараторы массы. Их стоимость гораздо ниже атомных, но для них всех находится работа в промышленности, торговле, стандартизации.

Общие сведения

Компаратор — это сравнивающее устройство. Аналоговый компаратор предназначен для сравнения непрерывно изменяющихся сигналов. Входные аналоговые сигналы компаратора суть Uвх — анализируемый сигнал и Uоп — опорный сигнал сравнения, а выходной Uвых — дискретный или логический сигнал, содержащий 1 бит информации:

| (1) |

Выходной сигнал компаратора почти всегда действует на входы логических цепей и потому согласуется по уровню и мощности с их входами. Таким образом, компаратор — это элемент перехода от аналоговых к цифровым сигналам, поэтому его иногда называют однобитным аналого-цифровым преобразователем.

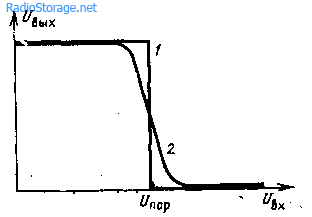

Неопределенность состояния выхода компаратора при нулевой разности входных сигналов нет необходимости уточнять, так как реальный компаратор всегда имеет либо конечный коэффициент усиления, либо петлю гистерезиса (рис. 1).

Рис. 1. Характеристики компараторов

Рис. 2. Процессы переключения компараторов

Чтобы выходной сигнал компаратора изменился на конечную величину |U 1 вых — U 0 вых| при бесконечно малом изменении входного сигнала, компаратор должен иметь бесконечно большой коэффициент усиления (эпюра 1 на рис. 2) при полном отсутствии шумов во входном сигнале. Такую характеристику можно имитировать двумя способами — или просто использовать усилитель с очень большим коэффициентом усиления, или ввести положительную обратную связь.

Рассмотрим первый путь. Как бы велико усиление не было, при Uвх близком к нулю характеристика будет иметь вид рис. 1а. Это приведет к двум неприятным последствиям. Прежде всего, при очень медленном изменении Uвх выходной сигнал также будет изменяться замедленно, что плохо отразится на работе последующих логических схем (эпюра 2 на рис. 2). Еще хуже то, что при таком медленном изменении Uвх около нуля выход компаратора может многократно с большой частотой менять свое состояние под действием помех (так называемый «дребезг», эпюра 3). Это приведет к ложным срабатываниям в логических элементах и к огромным динамическим потерям в силовых ключах. Для устранения этого явления обычно вводят положительную обратную связь, которая обеспечивает переходной характеристике компаратора гистерезис (рис. 1б). Наличие гистерезиса хотя и вызывает некоторую задержку в переключении компаратора (эпюра 4 на рис. 2), но существенно уменьшает или даже устраняет дребезг Uвых.

В качестве компаратора может быть использован операционный усилитель (ОУ) так, как это показано на рис. 3. Усилитель включен по схеме инвертирующего сумматора, однако, вместо резистора в цепи обратной связи включены параллельно стабилитрон VD1 и диод VD2.

Рис. 3. Схема компаратора на ОУ

Пусть R1 = R2. Если Uвх — Uоп > 0, то диод VD2 открыт и выходное напряжение схемы небольшое отрицательное, равное падению напряжения на открытом диоде. При Uвх — Uоп m А710 (отечественный аналог — 521СА2), разработанного Р. Видларом (R.J.Widlar) в США в 1965 г., приведена на рис. 4.

Рис. 4. Схема компаратора m А710

Она представляет собой дифференциальный усилитель на транзисторах VT1, VT2, нагруженный на каскады ОЭ на VT5 и VT6. Каскад на VT5 через транзистор VТ4 управляет коллекторным режимом входного каскада и через транзистор в диодном включении VТ7 фиксирует потенциал базы транзистора VT8, делая его независимым от изменений положительного напряжения питания. Каскад на VT6 представляет собой второй каскад усиления напряжения.

Эмиттерные выводы транзисторов VT5 и VT6 присоединены к стабилитрону VD1 с напряжением стабилизации 6,2 В, поэтому потенциалы баз указанных транзисторов соответствуют приблизительно 6,9 В. Следовательно, допустимое напряжение на входах компаратора относительно общей точки может достигать 7 В. На транзисторе VT8 выполнен эмиттерный повторитель, передающий сигнал с коллектора VT6 на выход. Постоянная составляющая сигнала уменьшается до нулевого уровня стабилитроном VD2.

Если дифференциальное входное напряжение превышает +5. +10 мВ, то транзистор VT6 закрыт, а VT5 близок к насыщению. Выходной сигнал компаратора при этом не может превысить +4 В, так как для более положительных сигналов открывается диод на VT7, не допуская излишнего роста выходного напряжения и насыщения VТ5. При обратном знаке входного напряжения VT6 насыщается, потенциал его коллектора оказывается близок к напряжению стабилизации стабилитронов VD1 и VD2, а поэтому потенциал выхода близок к нулю. Транзистор VT9 — источник тока 3 мА для смещения VT8 и VD2. Часть этого тока (до 1,6 мА) может отдаваться в нагрузку, требующую вытекающий ток на входе (один вход логики ТТЛ серии 155 или 133).

В дальнейшем эта схема развивалась и совершенствовалась. Схемы многих компараторов имеют стробирующий вход для синхронизации, а некоторые модификации снабжены на выходе триггерами-защелками, т.е. схемами, фиксирующими состояние выхода компаратора по приходу синхроимпульса. Кроме того, для повышения функциональной гибкости часть ИМС компараторов (например, МАХ917-920) содержит источник опорного напряжения, а у некоторых (например, МАХ910) порог срабатывания устанавливается цифровым кодом от 0 до 2,56 В с дискретностью 10 мВ , для чего на кристалле микросхемы имеются источник опорного напряжения и 8-разрядный цифро-аналоговый преобразователь.

Выходные каскады компараторов обычно обладают большей гибкостью, чем выходные каскады операционных усилителей. В обычном ОУ используют двухтактный выходной каскад, который обеспечивает размах напряжения в пределах между значениями напряжения питания (например, +/-13 В для ОУ типа 140УД7, работающего от источников +/-15 В). В выходном каскаде компаратора эмиттер, как правило, заземлен, и выходной сигнал снимается с «открытого коллектора». Выходные транзисторы некоторых типов компараторов, например, 521СА3 или LM311 имеют открытые, т.е. неподключенные, и коллектор и эмиттер. Две основные схемы включения компараторов такого типа приведены на рис. 5.

Рис. 5. Схемы включения выходного каскада компаратора 521СА3

На рис. 5а выходной транзистор компаратора включен по схеме с общим эмиттером. При потенциале на верхнем выводе резистора равном +5 В к выходу можно подключать входы ТТL, nМОП- и КМОП-логику с питанием от источника 5 В. Для управления КМОП-логикой с более высоким напряжением питания следует верхний вывод резистора подключить к источнику питания данной цифровой микросхемы.

Если требуется изменение выходного напряжения компаратора в пределах от U + пит до U — пит, выходной каскад включается по схеме эмиттерного повторителя (рис. 5б). При этом заметно снижается быстродействие компаратора и происходит инверсия его входов.

Некоторые модели интегральных компараторов (например, AD790, МАХ907) имеют внутреннюю неглубокую положительную обратную связь, обеспечивающую их переходной характеристике гистерезис с шириной петли, соизмеримой с напряжением смещения нуля.

На рис. 6а приведена схема включения компаратора с открытым коллектором на выходе, переходная характеристика которой имеет гистерезис (рис. 1б). Пороговые напряжения этой схемы определяются по формулам

,

,

Из-за несимметрии выхода компаратора петля гистерезиса оказывается несимметричной относительно опорного напряжения.

Рис. 6. Компаратор с положительной обратной связью

В заключение, перечислим некоторые особенности компараторов по сравнению с ОУ.

- Несмотря на то, что компараторы очень похожи на операционные усилители, в них почти никогда не используют отрицательную обратную связь, так как в этом случае весьма вероятно (а при наличии внутреннего гистерезиса — гарантировано) самовозбуждение компараторов.

- В связи с тем, что в схеме нет отрицательной обратной связи, напряжения на входах компаратора неодинаковы.

- Из-за отсутствия отрицательной обратной связи входное сопротивление компаратора относительно низко и может меняться при изменении входных сигналов.

- Выходное сопротивление компараторов значительно и различно для разной полярности выходного напряжения.

Двухпороговый компаратор

Двухпороговый компаратор (или компаратор «с окном») фиксирует, находится ли входное напряжение между двумя заданными пороговыми напряжениями или вне этого диапазона. Для реализации такой функции выходные сигналы двух компараторов необходимо подвергнуть операции логического умножения (рис. 7а). Как показано на рис. 7б, на выходе логического элемента единичный уровень сигнала будет иметь место тогда, когда выполняется условие U1 m А711 (отечественный аналог — 521СА1).

Рис. 7. Схема двухпорогового компаратора (а) и диаграмма его работы (б)

Параметры компараторов

Параметры, характеризующие качество компараторов, можно разделить на три группы: точностные, динамические и эксплуатационные.

Компаратор характеризуется теми же точностными параметрами, что и ОУ.

Основным динамическим параметром компаратора является время переключения tп. Это промежуток времени от начала сравнения до момента, когда выходное напряжение компаратора достигает противоположного логического уровня. Время переключения замеряется при постоянном опорном напряжении, подаваемом на один из входов компаратора и скачке входного напряжения Uвх, подаваемого на другой вход. Это время зависит от величины превышения Uвх над опорным напряжением. На рис. 8 приведены переходные характеристики компаратора mА710 для различных значений дифференциального входного напряжения Uд при общем скачке входного напряжения в 100 мВ. Время переключения компаратора tп можно разбить на две составляющие: время задержки tз и время нарастания до порога срабатывания логической схемы tн. В справочниках обычно приводится время переключения для значения дифференциального напряжения, равного 5 мВ после скачка.

Рис. 8. Переходная характеристика компаратора m А710 при различных превышениях скачка входного напряжения Uд над опорным: 1 — на 2 мВ; 2 — на 5 мВ; 3 — на 10 мВ; 4 — на 20 мВ

Пороговые устройства, называемые также компараторами, предназначены для преобразования аналогового сигнала в цифровую информацию. Например, на выходе порогового элемента формируется сигнал какого-либо логического уровня, если входной аналоговый сигнал по своему значению меньше определенного напряжения, если же он больше, то на выходе порогового устройства формируется сигнал противоположного логического уровня.

Кроме регистрации или сигнализации о превышении (или снижении) напряжения контролируемого сигнала, пороговые устройства применяют в аналого-цифровых преобразователях, генераторах импульсов различной формы.

В составе некоторых серий аналоговых микросхем есть компараторы, пригодные для совместной работы с цифровыми микросхемами, но они не всегда доступны. Многие из них требуют двухполярного источника питания, что усложняет конструкцию. Поэтому в ряде случаев оказывается целесообразным использовать в качестве пороговых устройств элементы, что обеспечивает полное согласование логических уровней без каких-либо специальных мер.

В принципе, сам элемент представляет собой пороговое устройство, в чем легко убедиться, взглянув на рис. 18, на котором показаны передаточные характеристики идеального порогового устройства 1 и элемента КМОП 2. У идеального порогового устройства прямоугольная характеристика, элемент же имеет характеристику с некоторым наклоном, поэтому вблизи порогового напряжения возникает зона неопределенности, которая в итоге и определяет чувствительность порогового устройства. В тех случаях, когда не требуется высокой точности, в качестве порогового устройства можно использовать логический элемент.

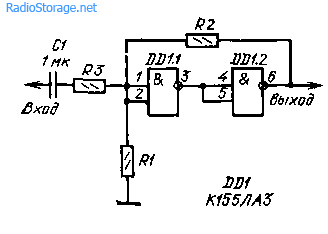

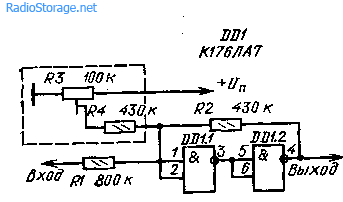

Для повышения точности пороговых устройств на основе элементов применяют специальные схемные решения. Схема простого порогового устройства на двух элементах ТТЛ приведена на рис. 19,а. Благодаря наличию положительной обратной связи (ПОС) по постоянному току через резистор R2 передаточная характеристика становится прямоугольной (рис. 19,6). Устройство работает следующим образом. При входном сигнале меньше порогового на выходе будет напряжение низкого уровня. С увеличением входного напряжения до U2 на выходе элемента DD1.2 напряжение также начнет увеличиваться. Это напряжение через резистор R2 поступит на вход элемента DD1.1, что приведет к еще большему увеличению напряжения на выходе элемента DD1.2 и т. д. Таким образом, пороговое устройство скачком переходит в устойчивое состояние с высоким уровнем напряжения на выходе. Дальнейшее увеличение входного напряжения состояние порогового устройства не изменяет.

Рис. 18. Характеристики порогового устройства и элемента КМОП

При уменьшении входного напряжения до U] пороговое устройство скачком переходит в устойчивое состояние с низким уровнем напряжения на выходе. Разность напряжений U2—U1 называют шириной петли гистерезиса, она зависит от соотношения номиналов резисторов R1 и R2. От этих же резисторов зависит и чувствительность. При увеличении сопротивления резистора R2 и уменьшении R1 чувствительность повышается, а ширина петли гистерезиса уменьшается. Однако элементы ТТЛ работают с входными токами, поэтому сопротивление этих резисторов должны лежать в определенных пределах. Так, для микросхем серий К133 и К155 сопротивление резистора R1 может быть в пределах 0,1 . 2 кОм, a R2 — в пределах 2. 10 кОм.

Такое пороговое устройство не имеет на входе разделительного конденсатора, поэтому нижняя граница его частотной характеристики простирается вплоть до постоянного напряжения, а вот верхняя, из-за наличия к цепи сигнала резистора R1, ограничена частотой 8. 10 МГц.

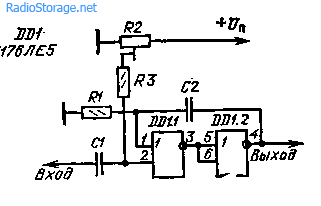

Если необходимо пороговое устройство, реагирующее только на переменную составляющую сигнала, его следует несколько изменить в соответствии с рис. 20. Сопротивления резисторов R2 и R3 должны быть примерно равны, емкость конденсатора С1 определяет нижнюю частотную границу рабочего диапазона.

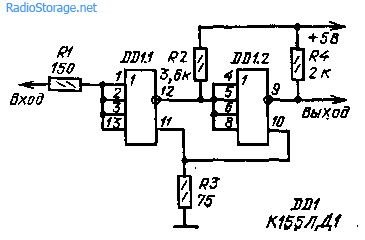

Большей граничной частотой обладает пороговое устройство на логических расширителях по ИЛИ микросхемы К155ЛД1 (рис. 21), по схемному построению аналогичное триггеру Шмитта на транзисторах. Порог срабатывания зависит от соотношения номиналов резисторов R1 и R3. Ширина петли гистерезиса составляет около 0,1 В, а порог срабатывания можно регулировать от 0,02 до і В. Номинал резистора SR1! должен быть в пределах 0,(1 . 1 кОм, a R2 — 22.

Рис. 19. Пороговое устройство на элементе ТТЛ

Рис. 20. Принципиальная схема порогового устройства на элементе ТТЛ

Рис. 21. Принципиальная схема порогового устройства на микросхеме К155ЛД1

Недостатком такого устройства является несколько повышенное, чем обычно, напряжение низкого логического уровня, за счет падения напряжения на резисторе R3.

Выполнить пороговый элемент можно и на элементах КМОП (рис. 22). Его отличительной особенностью является экономичность, а недостатком — низкая чувствительность. Поскольку элементы КМОП работают без входных токов и обладают невысокой нагрузочной способностью по току, то сопротивления резисторов R1 и R2 обычіно выбирают большими — десятки и сотни килорм. Для повышения чувствительности устройства на его вход следует подавать начальное смешение от источника питания через делитель R3R4.

При .контроле сигнала, уровень которого может изменяться в больших пределах, например музыкального сигнала, возможна ситуация, когда сигнал на очень короткое время превысит пороговое значение. Хотя устройство и сработает, но этого времени может не хватить, например, для включения индикатора. В таком случае будет полезным пороговое устройство с «памятью» (,рис. 23), которое на определенное время сохранит информацию о том, что сигнал превысил пороговое напряжение или был меньше него. От предыдущего устройства оно отличается тем, что в цепь ПОС между выходом элемента DD1.2 и одним из входов элемента DD1.1 включен конденсатор С2. Как только на выходе элемента DD1.2 появляется напряжение высокого уровня, оно через конденсатор С2 поступает на вход элемента DDL1. В таком состоянии устройство остается до тех пор, пока не зарядится этот конденсатор, даже в том случае, если уровень входного сигнала станет ниже порогового значения. Время, в течение которого информация о превышении сигнала хранится в устройстве, определяется постоянной времени цепи R1C2.

В каких же конструкциях можно применить пороговые устройства? В приборах, сигнализирующих об изменении напряжения, сигнала, в реле времени ^таймеры), различных индикаторах, генераторах и многих других. Цифровые микросхемы широко используют для генерирования сигналов с разными параметрами. Благодаря большому коэффициенту усиления н хорошим частотным свойствам на базе их логических элементов удается реализовать генераторы с частотой от долей герца до десятков и сотен мегагерц, к тому же самой различной формы.

Рис. 22. Принципиальная схема порогового устройства на элементе КМОП

Рис. 23. Принципиальная схема порогового устройства с «памятью»

Литература: И. А. Нечаев, Массовая Радио Библиотека (МРБ), Выпуск 1172, 1992 год.

mytooling.ru

Компараторы и триггеры Шмитта на ОУ

Всем доброго времени суток. В предыдущих статьях я рассказывал о применении операционных усилителей в линейных схемах, где ОУ охвачен отрицательной обратной связью, которая позволяет строить усилители, параметры которых будут в основном определяться элементами обвязки ОУ. Данная статья расскажет о применении ОУ без обратной связи или даже с положительной обратной связью (ПОС).

Работа операционного усилителя без обратной связи

Как известно напряжение на выходе ОУ UВЫХ определяется произведением входного дифференциального напряжения UД (разность напряжений между входными выводами) на коэффициент усиления ОУ по напряжению КU

Операционные усилители имеют очень большой коэффициент усиления ОУ по напряжению КU = 105 … 106, а выходное напряжение не может выйти за пределы напряжения питания (обычно несколько меньше). Поэтому, для того чтобы ОУ работал в качестве усилителя напряжения максимальное входное дифференциальное напряжение не должно превышать нескольких десятков мкВ (при UПИТ = 15 В, КU = 105, UД ≈ 150 мкВ). С учётом вышесказанного можно сделать вывод, что без применения отрицательной обратной связи, которая снижает усиление ОУ в схеме, применение ОУ бесполезно, так как при входных напряжениях в несколько милливольт ОУ войдёт в насыщение с выходным напряжением равным напряжению питания.

Но существуют схемы, в которых операционные усилители применяются без обратной отрицательной связи, а в некоторых случаях специально вводят положительную обратную связь (ПОС) для увеличения коэффициента усиления схем. Одним из видов таких схем являются пороговые устройства, в состав которых входят различные компараторы, триггеры Шмитта, детекторы уровней напряжения.

Принцип работы компаратора

Простейшим пороговым устройством является компаратор. Он сравнивает напряжение, которое поступает на один из его входов, с опорным напряжением, которое присутствует на другом его входе. Простейший компаратор получается из операционного усилителя, в котором отсутствует отрицательная обратная связь. Рассмотрим принцип работы компаратора напряжений на основе ОУ, схема которого изображена ниже

Использование ОУ в качестве компаратора и графики входного и выходного напряжений.

В основе компаратора лежит ОУ на инвертирующий вход, которого поступает входное напряжение UBX, а неинвертирующий вход соединён с источником опорного напряжения UОП. Принцип работы компаратора изображённого на рисунке заключается в следующем: когда входное напряжение UBX больше опорного UОП, то выходное напряжение принимает значение отрицательного напряжения насыщения –UНАС и остаётся неизменным пока входное напряжение UBX не уменьшиться ниже опорного напряжения UОП, в этом случае на выходе будет напряжение положительного насыщения +UНАС.

На рисунке изображен компаратор с инвертирующим выходным сигналом по отношению к входному сигналу. Для того, чтобы не происходило инверсии на выходе необходимо поменять подключение выводов ОУ, то есть входной сигнал должен поступать на неивертирующий вход, а опорное напряжение на инвертирующий вывод. Тогда при превышении опорного напряжения на выходе ОУ будет положительное напряжение насыщения, а при входном напряжении меньше, чем опорное напряжение на выходе будет присутствовать отрицательное напряжение насыщения ОУ.

Основные схемы компаратора

Существует много разновидностей компараторов, но в из основе лежат две основные схемы: одновходовая и двухвходовая. Одновходовая схема позволяет сравнивать разнополярные напряжения по модулю, то есть по абсолютной величине. Двухвходовый же компаратор сравнивает два напряжения с учётом знака. Расссмотрим обе схемы подробнее.

Схема одновходового компаратора.

На рисунке выше изображён одновоходовый компаратор, позволяющий сравнивать два разнополярных напряжения по абсолютному значению (по модулю). В его основе лежит инвертирующий сумматор, в котором отсутствует отрицательная обратная связь, поэтому ослабления коэффициент усиления операционного усилителя не происходит. В результате чего на инвертирующем входе ОУ происходит суммирование входного напряжения UBX и опорного напряжения UОП приведённого к инвертирующему входу UПРИВ, а результат суммирования усиливается ОУ и выводится на его выход. Для того чтобы происходило сравнение необходимо фактически производить операцию вычитания, то есть напряжения на входах UBX и UПРИВ должны иметь разную полярность.

Приведённое напряжение UПРИВ можно вычислить по следующему выражению

Резистор R3 предназначен для компенсации входного тока смещения и должен быть равен величине параллельно соединённых резисторов R1 и R2

Основным недостатком данной схемы является необходимость использования стабилизированного отрицательного напряжения, что приводит к усложнению схемы. Поэтому одновходовый компаратор не получил широкого распространения.

Наибольшее распространение получила схема двухвходового компаратора, в котором отсутствует необходимость в отрицательном напряжении. Схема данного компаратора приведена ниже

Схема двухвходового компаратора.

В основе двухвходового компаратора лежит дифференциальный усилитель, в котором отсутствует отрицательная обратная связь, поэтому разность между входным напряжением UBX и UОП опорным напряжение усиливается ОУ, не имеющего снижения коэффициента усиления из-за отсутствуя ООС, и выделяется на выходе ОУ. В данной схеме входные резисторы R1 и R2 имеют одинаковое значение.

Компараторы применяются в широком спектре схем:

- Триггеры Шмитта и в схемах формирования сигнала, преобразующих сигнал произвольной формы в прямоугольный или импульсный сигнал.

- Детекторы уровня – схемы, в которых происходит индицирование момента достижения входным сигналом заданного уровня опорного напряжения.

- Генераторы импульсных сигналов, например, треугольной или прямоугольной формы.

При использовании компаратора в схемах, где входное напряжение медленно меняется и амплитуда сигнала очень близка к опорному напряжению, то шумы на входном выводе могут вызвать ложные срабатывания компаратора и на его выходе могут появиться дополнительные импульсы, что продемонстрировано на рисунке ниже

Появление ложных импульсов на выходе компаратора.

Для устранения таких ложных срабатываний компаратора, в его схему вводится некоторый гистерезис, путём добавления положительной обратной связи (ПОС) к операционному усилителю.

Триггер Шмитта

Как сказано выше для устранения ложных срабатываний компаратора, известных, как «дребезг контактов» необходимо использовать схему компаратора с петлёй гистерезиса, которая получила название триггера Шмитта.

В одной из статей я рассказывал о триггере Шмитта выполненном на транзисторах. Он характеризуется тем, что в отличие от компаратора имеет так называемую петлю гистерезиса. То есть компаратор переключается из высокого уровня напряжения в низкий при одной и той же величине входного напряжения, а триггер Шмитта имеет два уровня (порога) переключения. Данное различие иллюстрирует изображение ниже

Изменение входного и выходного напряжения компаратора (справа) и триггера Шмитта (слева).

Уровни напряжения, при которых происходит переключение триггера Шмитта называются верхним уровнем (порогом) срабатывания триггера UВП и нижним уровнем (порогом) срабатывания триггера UНП.

Для реализации триггера Шмитта применяют ОУ охваченные положительной обратной связью (ПОС), которая реализуется подачей на неинвертирующий вход части выходного напряжения. Схема триггера Шмитта изображена ниже

Триггер Шмитта на операционном усилителе.

Работа триггера Шмитта во многом похожа на работу компаратора, только в отличие от него в триггере опорное напряжение не постоянно, а зависит от разности выходного и опорного напряжений, то есть имеет различные значения.

Рассмотрим инвертирующий триггер Шмитта. В исходном входное напряжение не превышает верхнего уровня срабатывания триггера UВП, поэтому на выходе присутствует положительное напряжение насыщения UНАС+ (примерно на 1 – 2 В ниже положительного напряжения питания UПИТ+). Когда входное напряжение достигает верхнего порога переключения UВП выходное напряжение резко упадёт до уровня отрицательного напряжения насыщения UНАС-(примерно на 1 – 2 В выше отрицательного напряжения питания UПИТ-). Верхний уровень напряжения переключения триггера Шмитта определяется следующим выражением

Далее триггер остаётся в устойчивом состоянии до тех пор, пока входное напряжение не станет меньше нижнего порога срабатывания UНП, а на выходе триггера установится положительное напряжение насыщения UНАС+. Нижний порог срабатывания триггера определяется следующим выражением

Таким образом, петля гистерезиса будет зависеть от соотношения резисторов R2 и R3, а ширина петли гистерезиса UГИС определяется разностью верхнего порога срабатывания UВП и нижнего порога срабатывания UНП

Триггеры Шмитта на ОУ являются основой для построения различных генераторов импульсов, поэтому важнейшими характеристиками ОУ работающих в импульсных схемах является быстродействие, которое зависит от задержек срабатывания и времени нарастания выходного напряжения.

Ограничение уровня выходного напряжения компаратора и триггера Шмитта

Применение положительной обратной связи (ПОС) в компараторах и триггерах Шмитта ускоряет переключение схем, но в связи с тем, что выходное напряжение UВЫХ изменяется от UНАС+ до UНАС-, то время переключения составляет довольно значительную величину (от долей до единиц микросекунд).

Кроме того существует проблема несовместимостей уровней выходного напряжения, к примеру, при напряжении питания ОУ UПИТ = ±15 В, выходное напряжение составит UВЫХ ≈ ±14 В (UНАС+ ≈ +14 В, а UНАС- ≈ -14 В), в то время как уровни ТТЛ микросхем составляют около +5 В или 0 В.

Для устранения вышеописанных проблем применяют так называемую привязку или ограничение уровня выходного напряжения, для этого в компаратор или триггер Шмитта вводят ООС в виде различных схем ограничения. Простейшими ограничительными схемами являются диоды или стабилитроны. Схема триггера Шмитта с ограничение выходного напряжения показана ниже

Триггер Шмитта с ограничением выходного напряжения при помощи стабилитрона в цепи ООС.

Ограничение выходного напряжения в триггере Шмитта работает следующим образом. При поступлении на инвертирующий вход напряжения меньше, чем напряжение опорного уровня (UВХОП), то выходное напряжение UВЫХ начинает изменяться в положительном направлении и при достижении напряжения стабилизации стабилитрона UСТ напряжение на выходе перестанет расти, а будет изменяться только ток. При этом выходное напряжение будет равняться напряжению стабилизации стабилитрона (UВЫХ = UСТ).

В случае если входное напряжение начнёт увеличиваться, выше опорного напряжения, то на выходе напряжение начнёт уменьшаться и в этом случае направление тока через стабилитрон начнёт изменяться на противоположный, а стабилитрон начнёт вести себя как диод. В результате падение напряжения на нём составит примерно 0,7 В независимо от величины протекающего через него тока, а на выходе напряжение составит -0,7 В.

Таким образом, при использовании стабилитрона выходное напряжение триггера Шмитта составит: UВЫХ1 = UСТ (при отсутствии ограничения UНАС+) или UВЫХ2 ≈ 0,7 (при отсутствии ограничения UНАС-).

Для симметричного ограничения выходного напряжения могут применяться последовательно включенные диоды или стабилитроны, что показано на рисунке ниже

Триггер Шмитта с симметричным ограничением выходного напряжения.

В данной схеме реализуется симметричное ограничение выходного напряжения относительно опорного напряжения, причем выходное напряжение выше опорного напряжения ограничивается стабилитроном VD1, а напряжение при этом составит на 0,7 В больше напряжения стабилизации. В случае же выходного напряжения ниже опорного, то выходное напряжение будет на 0,7 В ниже напряжения стабилизации стабилитрона VD2.

При расчёте компараторов и триггеров Шмитта с ограничением выходного напряжения в качестве UНАС+ необходимо использовать UСТ (когда используется один стабилитрон) или UСТVD1 (при двухстороннем ограничении). А вместо UНАС- необходимо использовать значение падения напряжения на диоде примерно 0,7 В (при одном стабилитроне) или UСТVD2 (при двухстороннем ограничении).

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

www.electronicsblog.ru

Компараторы цифровых сигналов

Сравнение кодированных сигналов осуществляется с помощью цифровых компараторов. Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном (двоично-десятичном) коде. В зависимости от схемного исполнения компараторы могут определять равенство А = В (А и В – независимые числа с равным количеством разрядов) либо определять вид неравенства: А < В или А > В. Результат сравнения отображается соответствующим логическим уровнем на выходе.

Цифровые компараторы широко применяются для выявления нужного числа (слова) в потоке цифровой информации, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, реализации программно управляемых приоритетов в системах прерывания компьютеров и т. д.

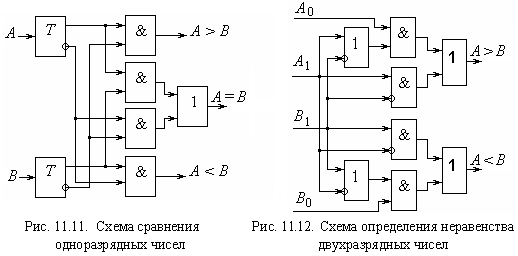

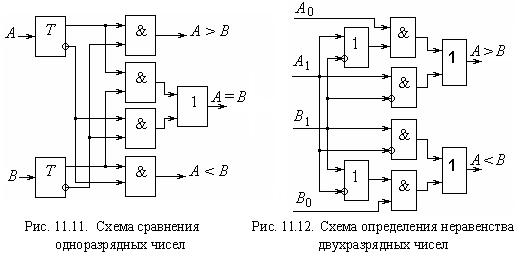

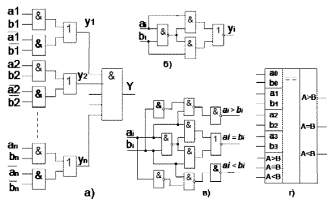

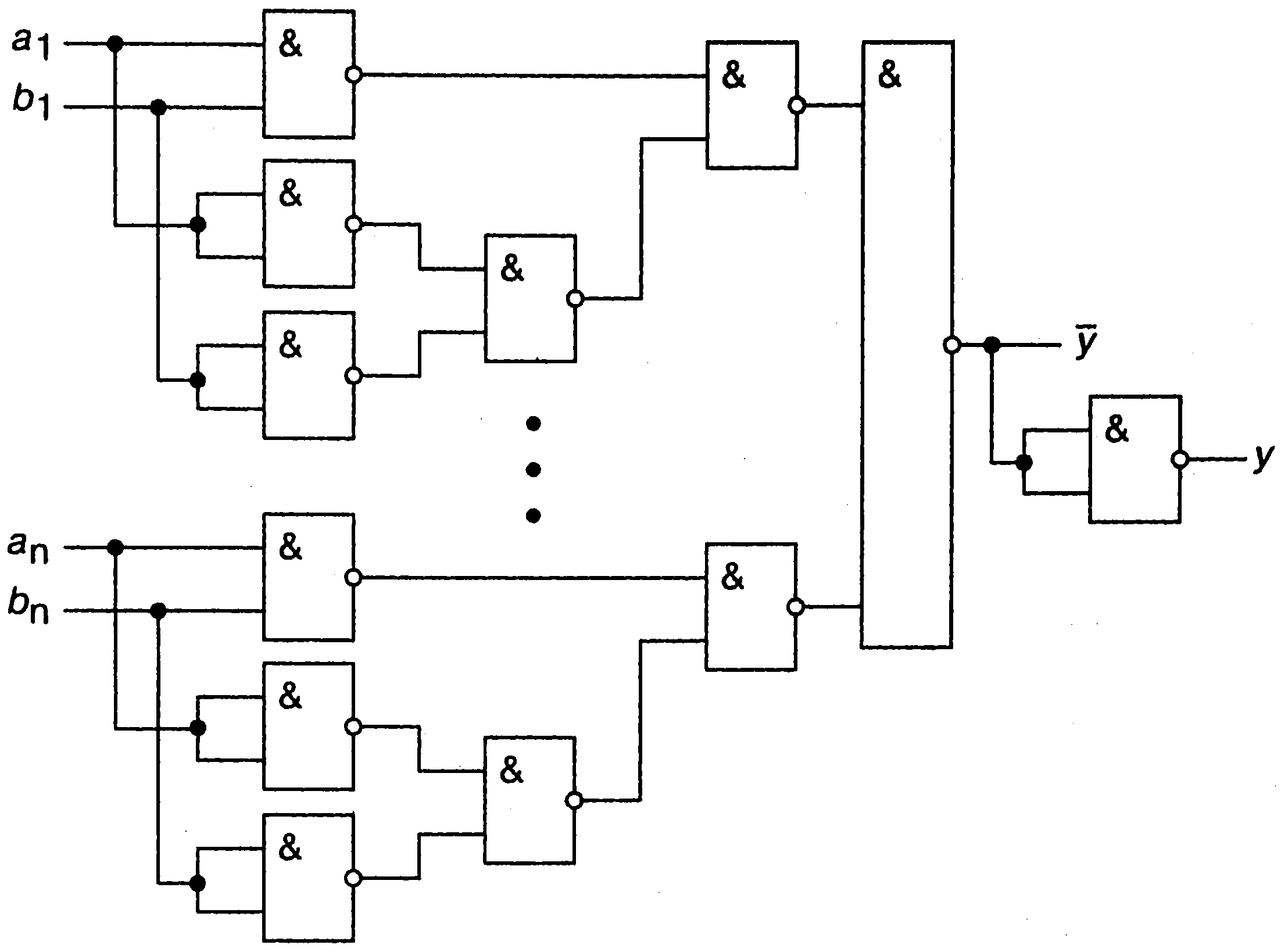

Ниже приведены схемы одноразрядного (рис. 11.11) и двухразрядного компараторов (рис. 11.12).

Рис. 11.11. схема сравнения одноразрядных чисел

Рис. 11.12. схема определения неравенства двухразрядных чисел

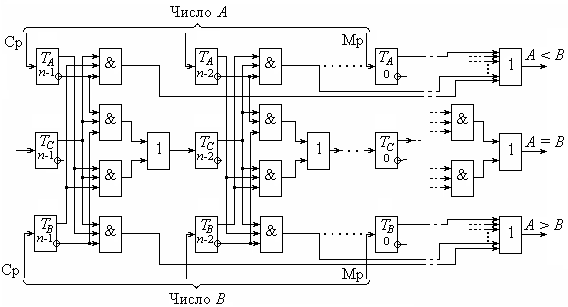

Многоразрядные компараторы строятся на базе одноразрядных. Применяют два способа построения многоразрядных компараторов. При первом способе сравнение идет последовательно разряд за разрядом. При появлении неравенства в каком-либо из разрядов, сравнение прекращается и выдается результат сравнения. Если неравенство оказывается в последнем разряде, то должна быть выполнена операция сравнения для всех разрядов. Это занимает много времени.

Схема сравнения многоразрядных чисел по первому способу представлена на рис. 11.13. Более быстрый способ – сравнение во всех разрядах одновременно и анализ результатов поразрядного сравнения.

Рис. 11.13. Схема сравнения многоразрядных чисел

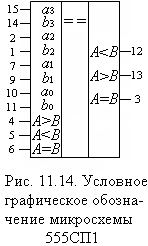

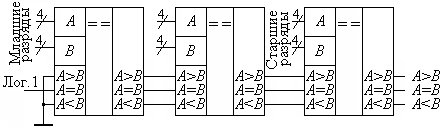

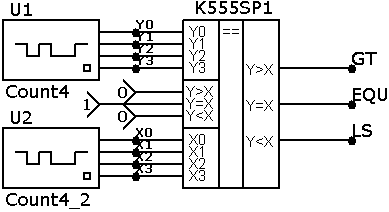

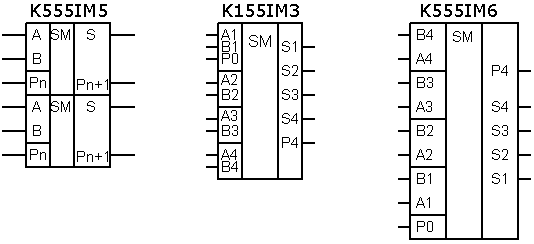

Нашей промышленностью выпускаются компараторы ТТЛ 555СП1, 531СП1, КМОП 561ИП2 и др. Компаратор 555СП1 – четырехразрядный, имеет 11 входов (рис. 11.14). Четыре пары входов принимают для анализа два четырехразрядных слова А0-А3 и В0-В3. Три входа (A < В), (A = В), (A > В) нужны для создания схемы наращивания, т. е. увеличения емкости компаратора. Компаратор имеет три выхода результатов анализа: A > В, A < В, A = В.

Соотношения входных и выходных сигналов компаратора представлены в табл. 11.6. Шесть последних строк таблицы отражают режим наращивания каскадов, который может быть последовательным или параллельным. При последовательном наращивании выходы A > В, A < В, A = В от схемы, анализирующей младшие разряды, следует присоединить к одноименным входам последующего каскада (рис. 11.15). Этим способом при двух компараторах СП1 можно сравнить два восьмиразрядных слова. Нетрудно подсчитать число каскадов для любой большей длины слова. Однако каждый последующий каскад увеличит общее время задержки распространения сигнала на 15 нс.

Рис. 11.14 Условное графическое обозначение микросхемы 555 СП1

Таблица 11.6

№ п.п. | Сравниваемые данные | Входы наращивания каскадов | Выходы | |||||||

а3, b3 | а2, b2 | аb, b1 | а0, b0 | A>B | A<B | A=B | A>B | A<B | A=B | |

1 | а3>b3 | X | X | X | X | X | X | 1 | 0 | 0 |

2 | а3<b3 | X | X | X | X | X | X | 0 | 1 | 0 |

3 | а3=b3 | а2>b2 | X | X | X | X | X | 1 | 0 | 0 |

4 | а3=b3 | а2<b2 | X | X | X | X | X | 0 | 1 | 0 |

5 | « | а2=b2 | a1>b1 | X | X | X | X | 1 | 0 | 0 |

6 | « | а2=b2 | a1<b1 | X | X | X | X | 0 | 1 | 0 |

7 | « | « | a1=b1 | а0>b0 | X | X | X | 1 | 0 | 0 |

8 | « | « | a1=b1 | а0<b0 | X | X | X | 0 | 1 | 0 |

9 | « | « | « | а0=b0 | 1 | 0 | 0 | 1 | 0 | 0 |

10 | « | « | « | а0=b0 | 0 | 1 | 0 | 0 | 1 | 0 |

11 | « | « | « | « | 0 | 0 | 1 | 0 | 0 | 1 |

12 | « | « | « | « | X | X | 1 | 0 | 0 | 1 |

13 | « | « | « | « | 1 | 1 | 0 | 0 | 0 | 0 |

14 | « | « | « | « | 0 | 0 | 0 | 1 | 1 | 1 |

Рис. 11.15. Последовательная схема объединения компараторов

Девятая и десятая строки табл. 11.6 говорят о том, что входы A > В и A < В могут служить пятой парой разрядных входов. Тогда одиночный компаратор можно использовать как пятиразрядный.

При применении компараторов надо учитывать, что при каскадировании задержки микросхем суммируются, и объединенный компаратор, состоящий из n микросхем, будет в n раз медленнее одиночного.

Если важен только факт равенства или неравенства сравниваемых кодов, то увеличить быстродействие при параллельном объединении компараторов можно, путём подачи их выходных сигналов A = В на логический элемент И (рис. 11.16). В этом случае суммарная задержка схемы составит задержку одного компаратора плюс задержку логического элемента И. Более подробные сведения о многокаскадных компараторах можно посмотреть, например, в [9, 11].

Рис. 11.16. Параллельная схема увеличения разрядности для оценки

равенства чисел

Компаратор КМОП серии 561ИП2 имеет несколько отличных режимов работы: например при всех низких уровнях входных сигналов A > В, A = В, A < В выходные A > В, A = В, A < В также низкие (у 555СП1 A > В и A < В высокие), т. е. для анализа работы компаратора надо использовать другую таблицу.

studfile.net

4.4 Устройства сравнения кодов. Цифровые компараторы

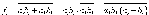

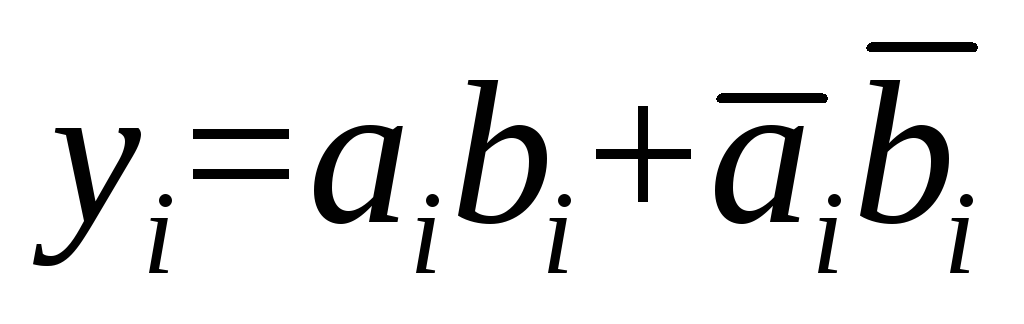

Устройства сравнения кодов предназначены для выработки выходного сигнала в случае, когда поступающие на их входы коды двух чисел оказываются одинаковыми.

Числа A

и B считаются равными, если разрядные

коэффициенты чисел A и B оказываются

одинаковыми, то есть, если ai=bi=1

или ai=bi=0.

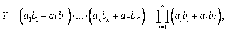

Эти равенства можно привести к одному:  .

Поскольку это равенство выполняется

для каждого разряда, то выходной сигнал

Y можно представить в виде логической

функции:

.

Поскольку это равенство выполняется

для каждого разряда, то выходной сигнал

Y можно представить в виде логической

функции:

где n — число разрядов.

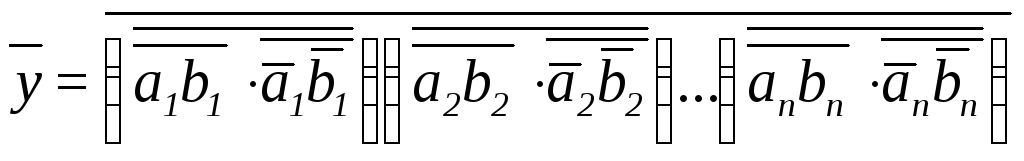

Рисунок 38 Устройства сравнения кодов: а) — структурная схема; б) — минимизированный вариант схемы сравнения в одном разряде; в) — одноразрядный компаратор; г) — УГО 4-разрядного компаратора.

Структурная схема устройства сравнения кодов, составленная на основании приведённого выше уравнения приведена на рисунке 38,а. Выходной сигнал Y=1 будет иметь место только при условии, если будут единичными результаты сравнения во всех разрядах сравниваемых чисел.

Недостатком рассмотренной схемы является большое число входов, так как для работы устройства требуются не только прямые, но и инверсные коды чисел A и В.

На основе законов алгебры логики разработаны устройства сравнения, работающие только с прямыми кодами.

Схема одноразрядного элемента сравнения, построенная на основании этого уравнения, приведена на рисунке 38,б. Функциональная схема, построенная на этих элементах, будет иметь вдвое меньшее число входов.

Цифровые компараторы являются универсальными элементами сравнения, которые помимо констатации равенства двух чисел, могут установить какое из них больше.

Простейшая задача состоит в сравнении двух одноразрядных чисел. Схема одноразрядного компаратора приведена на рисунке 38,в. При рассмотрении принципа работы схемы следует иметь в виду, что если ai < bi, то ai = 0, а bi = 1 и наоборот.

Для сравнения многоразрядных чисел используется следующий алгоритм. Сначала сравниваются значения старших разрядов. Если они различны, то эти разряды и определяют результат сравнения. Если они равны, то необходимо сравнивать следующие за ними младшие разряды, и т. д.

Цифровые компараторы выпускают в виде отдельных микросхем. Например, К561ИП2 позволяет сравнивать два 4-разрядных числа с определением знака неравенства. УГО этой МС приведено на рисунке 38,г.

Устройство обладает свойством наращиваемости разрядности сравниваемых чисел. Для сравнения, например, 8-разрядных чисел можно применить две четырёхразрядные микросхемы. Для этой цели в МС К561ИП2 предусмотрены три дополнительных входа: A > B, A = B и A > B, к которым подводятся соответствующие выходы микросхемы, выполняющей сравнение младших разрядов. Если используется только одна микросхема, то на вход A = B надо подать лог. «1», а на входы A < B и A > B — дог. «0».

4.5 Преобразователи кодов. Индикаторы

Операция изменения кода числа называется его преобразованием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов. Интегральные микросхемы преобразователей кодов выпускаются только для наиболее распространённых операций таких как преобразователи двоичного кода в десятичный, двоично-десятичный, шестнадцатеричный, код Грея или обратных, указанным выше, преобразований.

По своей структуре преобразователи кодов являются дешифраторами, только они преобразуют двоичный код в сигналы не только на одном, но и на нескольких выходах.

В качестве примера рассмотрим преобразователь двоичного кода в код управления 7-сегментным цифровым индикатором. На рисунке 39,а приведена схема подключения индикатора. Индикатор представляет собой полупроводниковый прибор, в котором имеется восемь сегментов, выполненных из светодиодов. Включением и выключением отдельных сегментов можно получить светящееся изображение отдельных цифр или знаков.

Конфигурация и расположение сегментов индикатора показаны на рисунке 39,а. Каждой цифре соответствует свой набор включения определённых сегментов индикатора. Соответствующая таблица отображения цифр и десятичной разделительной точки приведена на рисунке 39,б.

Рисунок 39 Преобразователь двоичного кода в код 7 – сегментного индикатора:

а) — Схема подключения индикатора; б) — Таблица состояний.

По внутренней схеме включения индикаторы подразделяются на индикаторы с общим катодом и с общим анодом. Схемы обоих видов индикаторов приведены на рисунке 40,а и 40,б соответственно.

Существует широкая гамма различных модификаций семисегментных индикаторов. Они отличаются друг от друга размерами, цветом свечения, яркостью, расположением выводов.

Рисунок 40 Схемы индикаторов: а) — с общим катодом; б) — с общим анодом.

Для управления индикатором с общим катодом используется, например, дешифратор К514ИД1, а с общим катодом — К514ИД2. Используются микросхемы дешифраторов и других серий, например, 176ИД2, 176ИД3, 564ИД4, 564ИД5, К133ПП1 и др.

Шкальные индикаторы (светящиеся столбики) представляют собой линейку светодиодов с одним общим анодом или катодом. Они являются аналогами щитовых измерительных приборов и служат для отображения непрерывно изменяющейся информации.

Светящиеся шкалы могут быть установлены на приборном щитке автомобиля или самолёта для индикации уровня горючего в баке, скорости движения и других параметров. Удобна конструкция в виде расположенных рядом столбиков для индикации величин с целью их сравнения.

Преобразователи двоичного кода в код управления шкальным индикатором обеспечивают перемещение светящегося пятна, определяемое двоичным кодом на адресном входе.

Матричные индикаторы представляют собой наборы светодиодов, расположенных по строкам и столбцам. Наиболее распространённые матричные индикаторы имеют 5 столбцов и 7 строк (формат 5×7). Количество светодиодов таких индикаторов равно 35. Для управления матричными индикаторами выпускаются микросхемы, в которых положение светодиода задаётся номерами строки и столбца, причём не все комбинации используются. Такие преобразователи кодов называются неполными. К ним относятся, например, микросхемы К155ИД8 и К155ИД9.

studfile.net

КОМПАРАТОРЫ И ПОЛИКОМПАРАТОРНЫЕ МИКРОСХЕМЫ в устройствах на микросхемах

Компараторами называют электронные устройства, предназначенные для сравнения двух или более электрических величин. Компараторы часто используют для преобразования аналогового сигнала в цифровой, а также для восстановления формы искаженных цифровых сигналов. Компаратор может использоваться в качестве порогового устройства, срабатывающего в случае, если входной контролируемый сигнал превысит по величине сигнал заданный, опорный.

По виду сравниваемых входных сигналов компараторы подразделяют на две группы: аналоговые; цифровые.

Учитывая специфику данной монографии, ограничимся описанием аналоговых компараторов.

Аналоговый компаратор можно представить как простейший однобитный аналого-цифровой преобразователь. Выходной сигнал такого компаратора представлен, как правило, двумя возможными значениями, соответствующими уровням входного сигнала больше или меньше некоторой заданной пользователем величины:

♦ уровнем логической единицы;

♦ уровнем логического нуля.

В связи с этим важнейшими характеристиками компаратора являются величина и стабильность уровня (порога) перехода устройства из одного стабильного состояния в другое.

Зависимость выходного напряжения компаратора UBbIX от уровня входного UBX можно представить как

где Uon — опорное напряжение (напряжение сравнения).

Или, иными словами,

Компараторы чаще всего используют в пороговых, релейных схемах, устройствах контроля критически значимых величин.

Помимо основного назначения компараторы способны работать в качестве генераторов импульсов, аналого-цифровых преобразователях, схемах согласования логических уровней, схемах очистки зашумленных цифровых сигналов и т. д. Менее распространены двух- или более пороговые компараторы, которые наиболее часто применяют в простых индикаторах уровня входного сигнала, например, в светодиодных шкалах.

Компараторы по своему назначению или особенностям строения можно подразделить на такие группы:

♦ высоковольтные;

♦ низковольтные;

♦ маломощные компараторы, в том числе с источником опорного напряжения, в качестве которого может быть использован ОУ;

♦ повышенной выходной мощности, в том числе с защитой от перегрузки;

♦ высокоскоростные или повышенного быстродействия;

♦ с открытом выходом, выходом на КМОП, транзисторнотранзисторной или эмиттерно-связанной логике;

♦ с выходом «rail to rail»;

♦ двух- и более скоростные с автоматическим переходом на экономичный режим работы;

♦ прецизионные;

♦ многопороговые;

♦ многоканальные;

♦ с гистерезисом;

♦ стробируемые;

♦ с цифро-аналоговым преобразователем;

♦ программируемые;

♦ прочие.

Примечание.

Как правило, заметный выигрыш по одному из параметров обуславливает не менее значимый проигрыш по другому параметру. Так; например, пониженное энергопотребление компаратора достигается за счет снижения его быстродействия.

Компараторы обычно не содержат элементов частотной коррекции, имеют передаточную характеристику релейного типа и поэтому не могут использоваться в качестве линейных усилителей аналоговых сигналов, например, в качестве ОУ В то же время компараторы широко применяют для сопряжения аналоговых и цифровых устройств, на их основе могут быть созданы эффективные усилители D-класса.

Как было показано ранее, в качестве компараторов могут быть использованы обычные операционные усилители, охваченные петлей положительной обратной связи. Порок такого решения — низкая нагрузочная способность подобных устройств, поскольку для управления энергоемкой нагрузкой требуется применение усилителей мощности.

Специализированные компараторы, ориентированные, в отличие от операционных усилителей, на решение узкого круга задач, отличаются:

♦ повышенной нагрузочной способностью;

♦ быстродействием;

♦ невозможностью работы в линейном режиме.

Схемы компараторов — детекторов нуля, работающих на положительных или отрицательных перепадах входного напряжения, показаны на рис. 18.1 и 18.2. Переходная характеристика UBblx = UBbDC (UBX ) идеального компаратора имеет строго прямоугольную форму. Реальная форма этой характеристики (рис. 18.1 и рис. 18.2), определяется конечной скоростью переходных процессов, неидеальностью работы компаратора и его элементов.

Примечание.

Отмечу, что в крайне узком диапазоне входных напряжений компаратор способен работать как усилитель с крайне высоким коэффициентом усиления (порядка 105—106 и более). Очевидно, что стабильность работы такого усилителя невелика, т. к. положение его рабочей точки в существенной мере зависит от температуры окружающей среды, стабильности источников питающих напряжений и других факторов.

При желании точку переключения состояния компаратора (порог срабатывания) можно сместить в любую сторону относительно нуля.

Пример компаратора со ступенчато переключаемым — плавно регулируемым порогом срабатывания приведен на рис. 18.3.

Порог переключения компараторов не является строго фиксированной величиной. Обычно напряжение переключения компаратора нестабильно и в процессе работы хаотически смещается в ту или иную сторону от заданного уровня. Амплитуда таких флуктуаций определяется: свойствами конкретного типа компаратора; его разновидности; качеством изготовления; температурой окружающей среды; внешними воздействиями.

Примечание.

В этой связи при построении прецизионных схем сравнения напряжений необходимо предусматривать минимизацию или нейтрализацию собственных шумов компаратора.

Неприятной особенностью работы компараторов является их работа при уровнях входных сигналов вблизи порога разрешения переключения. В этом случае, если входной сигнал сильно зашумлен, на выходе компаратора появляется последовательность дельтавидных или иглоподобных апериодических импульсов, вносящих обычно сбои в работу радиоэлектронной аппаратуры.

Для минимизации паразитного переключения компаратора в условиях его работы с зашумленными сигналами иногда применяют схемотехнический прием, заключающийся в преднамеренном искажении формы переходной характеристики. На переходной характеристике такого компаратора наблюдается отчетливо выраженный гистерезис.

Рис. 18.4. Схема компаратора с гистерезисом (триггера Шмитта)

На рис. 18.4 и 18.5 показаны схемы компараторов с искусственно организованными петлями гистерезиса. Ширину петли гистерезиса AUraCT можно определить из выраже-

Рис. 18.5. Схема компаратора с регулируемой шириной петли гистерезиса

напряжение ограничения компаратора. Напряжения переключения компаратора +U и -U относительно заданного (нулевого, рис. 18.4 и 18.5, уровня) можно определить по

формуле

Компаратор уровней сигнала по амплитуде позволяет сопоставить величину (уровень) двух сигналов и переключить свой выходной уровень с логической единицы на нуль (или наоборот) в случае, если входной сигнал превысит заданный порог срабатывания компаратора.

Рис. 78.7. Схема нерегулируемого двухпорогового компаратора напряжения

Рис. 78.6. Схема двухпорогового компаратора на операционном усилителе

Отдельной проблемой сопоставления уровней сигналов является задача двух- или многопорогового разделения сигналов. Варианты решения такой задачи показаны на рис. 18.6, 18.7 [18.1]. Зависимость выхо дного сигнала от уровня входного показана на рис. 18.7.

Порог переключения компаратора Όι (рис. 18.7) устанавливают подачей напряжения Uynp. В случае, если на вход компаратора подается высокое отрицательное напряжение, то оно действует только на инвертирующий вход микросхемы DA1.

При снижении уровня входного напряжения до значения

где UVD1=0,6—0,7 В (падение напряжения на кремниевом диоде VD1), на выходе ОУ установится положительное напряжение, рис. 18.7.

При дальнейшем возрастании уровня входного напряжения вплоть до значения U2 выходное напряжение компаратора имеет уровень логической единицы. Однако, при UBx >U2 диод VD1 более не шунтирует вход ОУ, компаратор вновь переключается, на его выходе устанавливается уровень логического нуля.

Для того, чтобы плавно управлять порогом переключения компаратора, может быть использована схема, рис. 18.8 [18.1]. Потенциометром R3 устанавливают порог переключения компаратора. Ширину зоны чувствительности компаратора регулируют потенциометром R2:

Сдвоенный компаратор К1464СА1

Рис. 78.8. Схема регулируемого компаратора напряжения

[18.2] (аналог LM193, LM293, LM393, LM2903 фирмы Philips, SGS-Thomson Microelectronics и NS [18.3]) отличается от иных:

♦ малой потребляемой мощностью;

♦ возможностью сравнивать сигналы, близкие к нулевому уровню.

Рис. 78.9. Состав и цоколевка микросхемы сдвоенного компаратора К1464СА1

Компаратор (рис. 18.9) работает при напряжении питания 2—36 В (однополярное) и 2±(1 —18) В (двуполярное питание) [18.2, 18.3]. Потребляемый ток менее 1 мА при напряжении питания 5 В и 2,5 мА при 36 В. Выходной ток — свыше 6 мА. Входное напряжение смещения не свыше 7 мВ при токе до 0,25 мкА. Выходные сигналы компаратора совместимы при работе с ТТЛ, ЭС77, КМОП- логическими элементами.

Примечание.

Отмечу, что перечисленные микросхемы отличаются лишь температурной областью устойчивой работы (температурный диапазон сужается от LM193K LM393).

На следующих рисунках показаны примеры практического использования микросхемы К1464СА1 (использован лишь один из двух компараторов) [18.2].

пор.н. ^ ^пор.в.’

Типовые схемы инвертирующего и неинвертирующего компараторов на микросхеме К1464СА1 приведены на рис. 18.10 и рис. 18.11. Значения нижнего и верхнего входного порогового напряжения U, рис. 18.10, определяется как [18.2]:

Рис. 18.14. Схема совместного использования компараторов LM 193, LM293, LM393, К1464СА1 сТТЛ и КМОП- логическими элементами

Рис. 18.10. Схема инвертирующего компаратора на микросхеме К1464СА1

Рис. 18.11. Схема неинвертирующего компаратора на микросхеме К1464СА1

Unop.H Unop в Unop.H Unop.в

Рис. 18.12. Передаточные характеристики компараторов

Рис. 18.13. Компаратор на микросхеме LM193, LM293, LM393, К1464СА1

При R1=R2=R3 UnopH * UniiT /3, UnopB * 2Unm /3, что примерно совпадает с соответствующими уровнями переключения из одного устойчивого состояния в другое для КМОП-микросхем. Передаточные характеристики инвертирующего и неинвертирующего компараторов показаны на рис. 18.12.

Типовая схема использования микросхем LM193, LM293, LM393, К1464СА1 в качестве компаратора показана на рис. 18.13 [18.3].

На рис. 18.14 показаны типовые схемы использования компараторов с микросхемами ТТЛ и КМОП-серий.

На рис. 18.15 показана схема выделения прохождения сигнала через ноль: при каждом прохождении входного напряжения через ноль детектор вырабатывает короткий импульс

[18.2]. В устройстве также использован инвертирующий компаратор напряжения с гистерезисом. Диод VD1 защищает входные цепи компаратора при появлении на входе минусовых полупериодов сигнала. Напряжение питания устройства 5 В.

На рис. 18.16 и рис. 18.17 показаны примеры использования компараторов в качестве НЧ усилителей с малой (рис. 18.16) и повышенной (рис. 18.17) нагрузочной способностью [18.3]. Коэффициент передачи усилителей определяется соотношением резистивных элементов R3/R2 и равен 100.

Рис. 18.18. Схема преобразователя- индикатора магнитного поля на компараторе LM393

Рис. 18.17. Схема НЧ усилителя на компараторе LM393 с повышенной нагрузочной способностью

Рис. 18.16. Схема НЧ усилителя на компараторе LM393

Рис. 78.75. Схема детектора «нуля».

На основе компараторов серии LM193, LM293, LM393, К1464СА1 может быть изготовлен преобразователь– индикатор магнитного поля, использующий в качестве датчика катушку индуктивности L1, рис. 18.18 [18.3].

Преобразователи амплитуды входного сигнала в ширину выходного используют в измерительной технике, импульсных блоках питания, цифровых усилителях.

На рис. 18.19,18.20 приведены схемы преобразователей амплитуды в ширину импульса [18.4]. Преобразователи выполнены на основе компараторов DA1 — К554САЗ. Напряжение на входах компаратора примерно равно половине напряжения питания (задается резистивным делителем R1/R2) и различается на величину напряжения, падающего на открытом переходе диода VD1. Входное сопротивление преобразователя равно Rl(R2)/2 или 25 кОм.

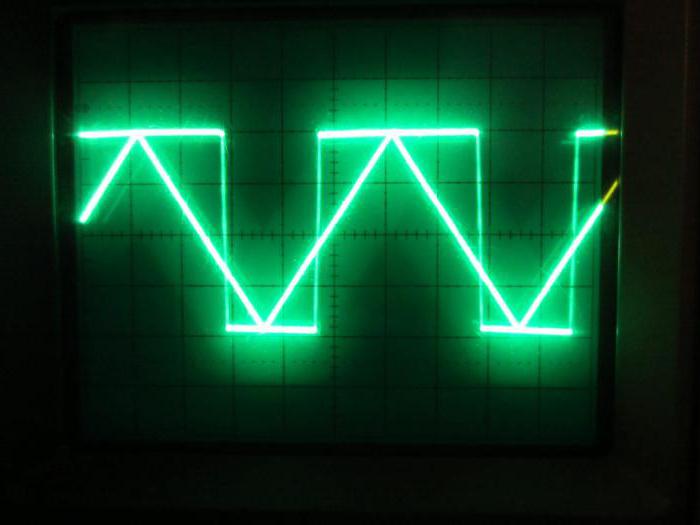

При подаче на вход синусоидального сигнала или сигнала пилообразной, треугольной формы и увеличении амплитуды, начиная с некоторого порогового значения, на выходе устройства формируются прямоугольные импульсы, ширина которых зависит от амплитуды входного сигнала. Схемы не требуют настройки. Полоса рабочих частот (область низких частот) определяется емкостью конденсаторов С1 и С2.

Устройства (рис. 18.19,

Рис. 18.79. Схема преобразователя амплитуды входного сигнала в ширину выходного на компараторе К554САЗ

18.20) отличаются способом подключения входов компаратора и, соответственно,

«полярностью» выходных сигналов. Частотная зависимость порогового напряжения начала работы преобразователей при использовании Si и Ge-диодов VD1 показана на рис. 18.21.

Для Ge-диодов (Д9Г) пороговое напряжение в полосе частот 5—200 кГц составляет 80—90 мВ, для Si (КД503А) — 250—270 мВ. Максимальная амплитуда входного сигнала — 2—2,5 В. При уменьшении номиналов резисторов R1 и R2 чувствительность устройства возрастает за счет снижения прямого напряжения на диоде VD1, одновременно снижается и входное сопротивление.

Преобразователь напряжения в частоту, схема которого представлена на рис. 18.22, позволяет при изменении входного напряжения от 0 до 5 В получить на выходе линейное увеличение частоты от О до 21 кГц (коэффициент преобразования 4,2 кГц/В с нелинейностью не свыше 3%) [18.5].

Таймер на микросхеме DA1 КР1006ВИ1 включен по схеме мультивибратора, времязадающий резистор которого заменен генератором тока на операционном усилителе DA1 741 (К140УД7).

Рис. 18.23. Схема прецизионного преобразователя напряжение-частота

Для получения высокой линейности преобразования отклонение сопротивление резисторов от номинала не должно превышать 0,5 %.

Помимо основного назначения — усиления сигналов, микросхема К1464УД1 может быть использована и в устройствах иного назначения, например, для преобразования напряжения входного сигнала в частоту выходного.

Преобразователь напряжение-частота (рис. 18.23) содержит управляемый генератор из интегратора на ОУ DA1.1 и компаратора с гистерезисом на ОУ DA1.2 [18.6]. На выходе интегратора формируется линейно изменяющееся во времени напряжение, скорость нарастания которого зависит от уровня входного напряжения UBX, а направление изменения — от состояния выхода компаратора DA1.2.

На выходе преобразователя формируется последовательность импульсов прямоугольной формы, частота которых прямо пропорционально зависит от уровня входного напряжения (0—3,5 В).

На основе ОУ КР140УД1208, который работает в диапазоне питающих напряжений ±1,5…±18 В при коэффициенте усиления до 200000, может быть собрано множество конструкций, в том числе устройств сравнения, часть из которых представлена на рис. 18.24—18.26 [18.7].

Примечание.

Микросхема выгодно отличается тем, что имеет защиту от короткого замыкания в цепи нагрузки.

Рис. 18.24. Схема индикатора разрядки батареи на микросхеме КР140УД1208

Индикатор разрядки батареи, рис. 18.24, содержит узел сравнения текущего значения контролируемого напряжения с некоторым образцовым значением. Для формирования образцового

напряжения использован узел, выполненный на транзисторе VT1. При достижении критического уровня напряжения, устанавливаемого при помощи потенциометра R9, включается генератор звуковых сигналов, выполненный на микросхеме DA1. В качестве излучателя звука использован пьезокерамический излучатель BF1 (ЗП-З).

Рис. 18.25. Упрощенный вариант индикатора разрядки батарей с визуальной индикацией

Емкость конденсатора С1 подбирают по максимальной громкости звучания пьезокерамического излучателя (настройка на его резонансную частоту).

Упрощенный вариант индикатора со светодиодной индикацией показан на рис. 18.25. Порог срабатывания (6,5 В) подбирают регулировкой потенциометра R2. Ток «молчания» индикаторов — 0,1 мА, индикации — 1 мА.

Индикатор электрического поля, схема которого представлена на рис. 18.26, предназначен для дистанционного бесконтактного контроля уровня электрического поля при приближении обслуживающего персонала к токонесущим конструкциям высокого напряжения.

В качестве антенны, определяющей чувствительность устройства, использована пластинка из фольгированного стеклотекстолита 55×33 мм, спрятанная в корпусе. Прибор срабатывает при приближении антенны к проводке под напряжением 220 В на расстояние не менее 50 см.

Совет.

Последовательно со светодиодом HL1 и капсюлем BF1 полезно включить токоограничивающий резистор сопротивлением до 300 Ом.

Рис. 18.26. Схема аудиовизуального индикатора электрического поля на микросхеме КР140УД1208

На основе компаратора DA1 КР554САЗБ может быть собрана схема фото- или термочувствительного реле, рис. 18.27 [18.8]. В первой из схем

(слева) в качестве светочувствительного элемента использован фотодиод VD1 КФДМ (или иной), входящий в состав сбалансированного резистивного моста. Балансировку моста осуществляют регулировкой потенциометра R2. К диагонали моста подключены входы компаратора DA1. Схема отрегулирована таким образом, чтобы при изменении уровня светового потока, падающего на приемную площадку фотоприемника, происходило переключение компаратора.

Примечание.

Если перед светочувствительным элементом установить светофильтр, можно создать прибор, чувствительный к излучению в определенной области спектра. Если использовать поляризационный светофильтр, прибор будет реагировать только на световой поток соответствующей поляризации. Такие устройства можно использовать, например, для автоматического открывания дверей ворот или гаража, когда к ним подъезжает автомобиль хозяина. Для повышения надежности срабатывания реле можно воспользоваться схемой совпадения, таким образом, реле будет срабатывать, если свойства сигнала-ключа будут отвечать, по меньшей мере, двум ключевым признакам.

В качестве нагрузки в реле [18.8] использовано оптоэлектронное реле 5П19.10ТМА-3-6, коммутирующее лампу накаливания, либо иную другую нагрузку.

Рис. 18.27. Схема фото- или термочувствительного реле на компараторе КР554САЗБ

Совет.

Вместо оптоэлектронного можно использовать и обычное электромагнитное реле с током срабатывания до 50 мА, обмотку которого в целях защиты выходного транзистора компаратора следует защитить параллельно подключенным диодом или электролитическим конденсатором.

Светодиод HL1 предназначен для визуального контроля момента срабатывания компаратора.

При желании фото- чувствительное реле (рис. 18.27, слева) легко преобразовывать в термочувствительное (рис. 18.27, справа). В качестве термочувствительного элемента можно использовать обычный кремниевый диод VD1, например, КД103А>

КД102А и др. Для снижения инерционности контроля в качестве датчика следует выбирать диод с минимальной массой.

Несколько модифицировав схему (рис. 18.27), можно получить реле времени для использования освещения подъездов и лестничных клеток, рис. 18.28 [18.8].

При кратковременном нажатии на любую из параллельно установленных на каждом этаже кнопок SB1—SBn кратковременно (на время, определяемое произведением R1C2), примерно на 60 с, включится лампа накаливания. Конденсатор С2 должен иметь малый ток утечки.

Пороговый индикатор превышения заданного уровня температуры, схема которого представлена на рис. 18.29 [18.9], может быть использован для автоматического регулирования теплового режима теплиц, инкубаторов, нагревательных узлов, систем сигнализации и т. д.

В устройстве использован компаратор DA1, нагруженный на светодиодный излучатель HL1. Питание индикатора стабилизировано. В качестве датчика температуры использован терморезистор R3 (или иной датчик). Рабочая точка (температура срабатывания) задается регулировкой потенциометра R4. Схему легко настроить на включение или отключении нагрузки (индикатора), поменяв его входы местами. В качестве датчика можно использовать, при необходимости, элементы, чувствительные к изменению освещенности (фоторезисторы), электрического поля (полевые транзисторы) и т. д.

Генератор на основе инвертирующего компаратора напряжения с гистерезисом на микросхеме К1464СА1, рис. 18.30,

вырабатывает короткие импульсы прямоугольной формы частотой 16 кГц [18.2]. Длительность импульса равна 0,7R4C1, паузы — 0,7R1C1, следовательно, период импульсов равен 0,7C1(R4+R1), а частота — 1,44/Cl (R4+R1).

Рис. 18.31. Схема удвоителя частоты на основе компараторе

Рис. 18.30. Схема генератора прямоугольных импульсов на компараторе

Пороговое устройство–компаратор может быть использовано в качестве широкодиапазонного (в определенных пределах) удвоителя частоты сигналов, рис. 18.31 [18.10]. Работа устройства основана на запоминании уровня сигналов на том или ином входе компаратора и последующем динамическом сопоставлении их уровня в ходе переходных процессов при заряде/раз- ряде конденсаторов.

В итоге на выходе устройства формируется последовательность импульсов с удвоенной по отношению к входному сигналу частотой, рис. 18.32. Входной сигнал имеет частоту 500—1000 Гц при амплитуде до 10 В.

Для иных частот потребуется подбор RC-элементов входных цепей.

Рис. 18.32. Входные и выходные сигналы удвоителя частоты на основе компараторе

Рис. 18.33. Схема устройства защиты от перенапряжения

Простое устройство (рис. 18.33) предназначено для защиты радиоэлектронного оборудования от недопустимых перепадов напряжения [18.11]. При снижении напряжения на входе устройства ниже некоторого заданного при помощи потенциометра R4 уровня сработает реле, отключив/подклю- чив своими контактами нагрузку, элемент защиты или стабилизации и т. п.

В качестве стабилитрона VD1 можно использовать стабилитрон на напряжение 3,3—5,1 В. Величина сопротивления R1 вычисляется исходя из того, чтобы напряжение на входном резистивном делителе R1—R2 примерно соответствовало напряжению на его движке, установленном посередине (т. е. примерно 2,4 В для стабилитрона КС147). Рассчитать

U, -U,

величину этого сопротивления можно из выражения: Rl=——-R2,

где Uj — входное напряжение срабатывания устройства, U2 — напряжение, примерно равное 2,4 В для стабилитрона КС147. Так, для 1^=100 В Rl=407 (390) кОм.

Напряжение питания устройства может быть выбрано в пределах 9—24 В. Следует лишь учитывать, чтобы реле надежно и без гистерезиса переключалось, а элементы схемы работали без перегрузок. На практике устройство можно использовать для автоматической записи телефонных разговоров. В этом случае параллельно резистору R2 рекомендуется подключить электролитический конденсатор емкостью не менее 100 мкФ.

Схема включения компаратора, рис. 18.34 [18.3], позволяет за счет наличия в его входных цепях RC-элементов отфильтровывать высокочастотные (R2C1) и низкочастотные (R1C2) наводки на полезный сигнал.

Пороговое устройство для слежения за температурным режимом, рис. 18.35, выполнено на микросхеме LM393 [18.12]. В качестве датчика температуры использован терморезистор R2, имеющий отрицательный температурный коэффициент. Для измерений используется традиционная мостовая резистивная схема.

Для сравнений уровней напряжения на диагонали моста использован компаратор. Порог срабатывания компаратора плавно регулируют потенциометром R4. Для звуковой индикации используют зуммер BF1 с пятивольтовым питанием (или заменяющий его мультивибратор с телефонным капсюлем в цепи нагрузки).

Рекомендуемые уровни напря

жений: 4,9 В — на выводе 5 микросхемы; 2,9 В — на выводе 6.

Параллельно шинам питания включают электролитический (470 мкФ) и керамический (0,1 мкФ) конденсаторы.

С использованием линейки однотипных компараторов (рис. 18.36) можно получить устройство светодиодной индикации уровня входного сигнала, например, радиоприемника, аудиоплеера [18.13]. Сетка опорных напряжений образуется на резистивном делителе R1—R9, образованном однономинальными резисторами. Входное напряжение поступает на неинвертирующие входы всех компараторов одновременно.

По мере повышения уровня входного напряжения поочередно будут высвечиваться светодиоды снизу вверх (по схеме), визуально в соответствии с уровнем входного сигнала будет перемещаться вверх-вниз или влево-вправо светящаяся точка, динамически показывающая уровень сигнала на входе устройства.

Чувствительность индикатора можно варьировать, подбирая соотношение номиналов входного резистивного делителя R10/R11.

Вход устройства можно подключить к движку потенциометра узла электронной настройки радиоприемника. В этом случае светодиодная шкала будет индицировать частоту приема, что особенно удобно при эксплуатации радиоприемника или передатчика в темное время суток.